https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1370231/sn65hvd24

器件型号:SN65HVD24工具与软件:

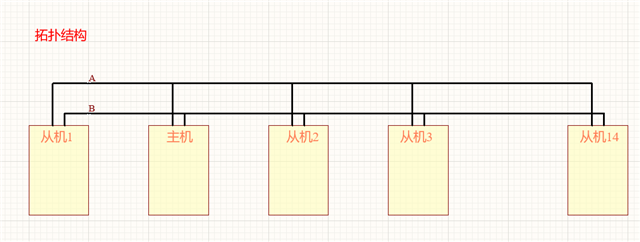

1 μ。应用架构:受限于产品架构,从机1没有完全按照菊花链架构设计,属于设计缺陷;各节点之间通过20cm的排线连接(非屏蔽双绞线)。A

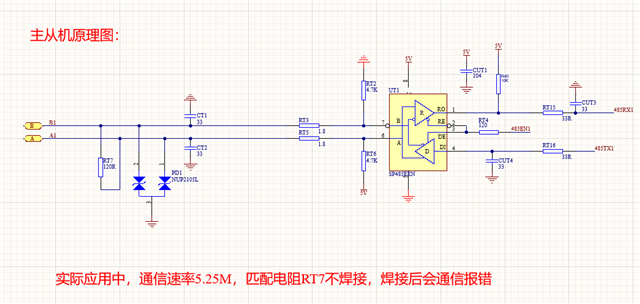

2 μ A。节点原理:

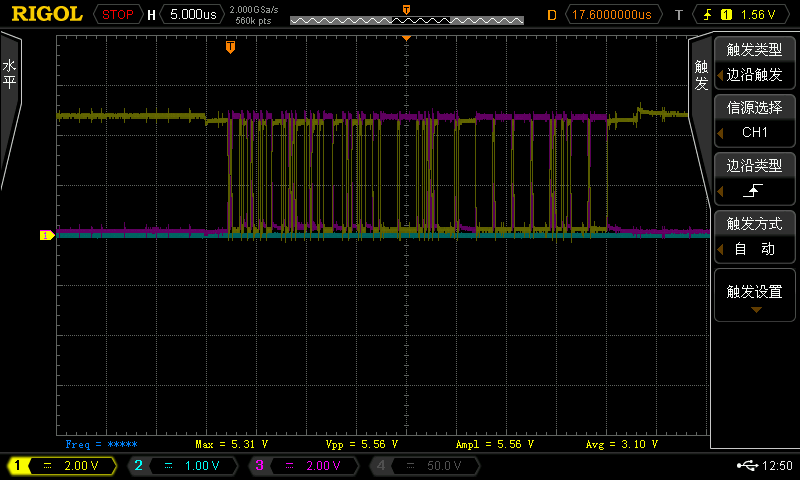

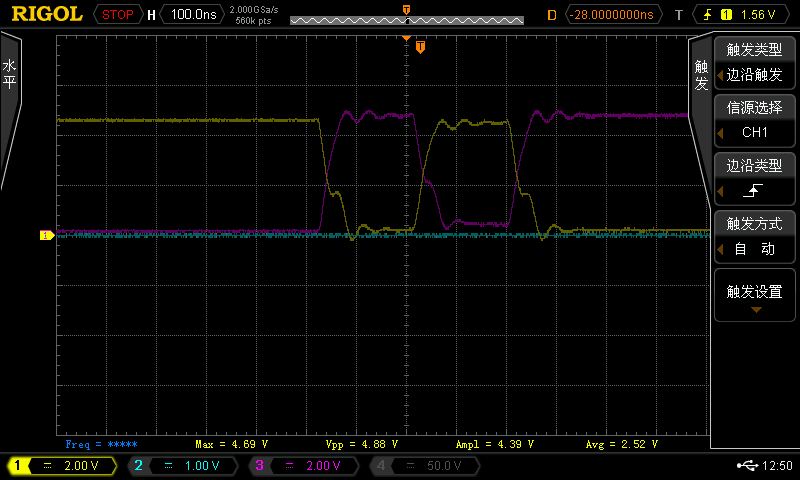

测试主机带单节点时的AB波形:μ A

问题:μ A (__LW_AT__1)μ A 这颗芯片这样使用(架构、连接方式、速率)是否合适,虽然可以正常通信,但总感觉和芯片手册推荐的电路差距有些大; (__LW_AT__2)波形并不是标准方波,且存在变形,如何进行进一步优化;(3)收发使能信号切换时,对波形有一定的影响,虽然没影响通信,但如何降低影响(4)在上述情况下为何加了匹配电阻(去掉上下拉电阻后)会报错,匹配电阻到底什么时候加