主题中讨论的其他器件:SN65DSI86、 TEST2

工具与软件:

您好、TI 团队、

我们 使用 SN65DSI86来显示色条图形、但仅显示黑色。 寄存器0x96的值为0x00、寄存器0xF8的值为0x12。 链路训练失败。

我们使用的 DP 通道数为4、DP 数据速率为1.62Gbps。

我们想更改"Link Training Look-Up-Table"默认值、您可以提供相同的建议 、说明合适的值是什么。

此致

艾米莉

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、TI 团队、

我们 使用 SN65DSI86来显示色条图形、但仅显示黑色。 寄存器0x96的值为0x00、寄存器0xF8的值为0x12。 链路训练失败。

我们使用的 DP 通道数为4、DP 数据速率为1.62Gbps。

我们想更改"Link Training Look-Up-Table"默认值、您可以提供相同的建议 、说明合适的值是什么。

此致

艾米莉

您好, David,

我们在 SN65DSI86和显示器之间使用的 FPC 为单层、而不是差分接线。 这是导致链路训练失败的原因吗?

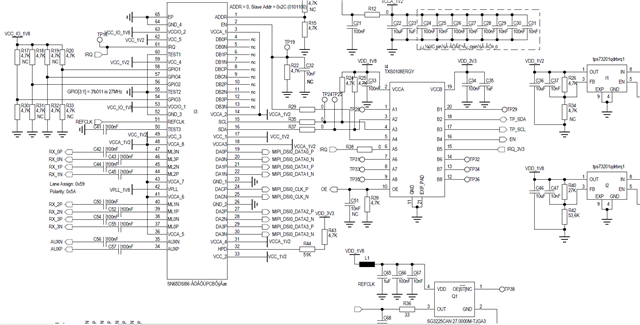

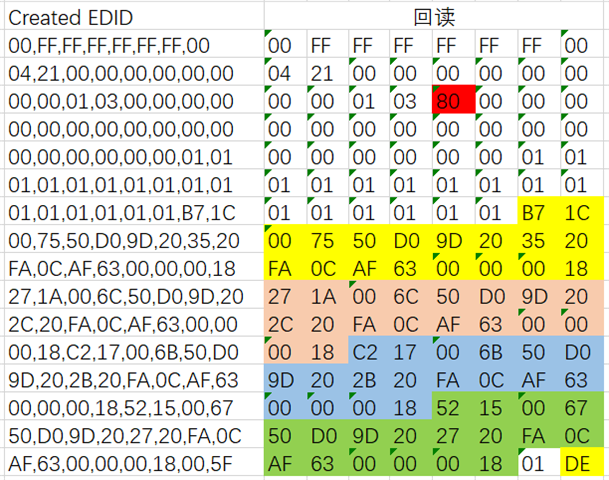

原理图、eDP/DP 分辨率 EDID 和 DSI86-Q1寄存器编程值如下所示。

我们 通过4.7k 电阻将 TEST2引脚拉至1.8V。

ADD = 0x0A;//ref clk 27M Hz

regmap_write (pdata->regmap、add、0x06);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

ADD = 0x5C;//禁用 HDP

regmap_write (pdata->regmap、add、0x00);

DRM_ERROR ("IIC 设置添加%x val 00\n"、添加);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

ADD = 0xE9;//启用 FAIL 整数

regmap_write (pdata->regmap、add、0xFF);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

ADD = 0x10;// 4个 DSI 通道

regmap_write (pdata->regmap、add、0x26);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

ADD = 0x12;// DSI CLOCK = freq 221Mhz

regmap_write (pdata->regmap、add、0x2C);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

ADD = 0x59;//aling 为3210

regmap_write (pdata->regmap、add、0x1B);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

regmap_write (pdata->regmap、0xff、0x07);

regmap_write (pdata->regmap、0x16、0x01);

regmap_write (pdata->regmap、0xff、0x00);

ADD = 0x5A;//F4 POLOR 增强帧和 ASSR

regmap_write (pdata->regmap、add、0xF4);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

添加= 0x93;//4 DP 通道、无 SCC

regmap_write (pdata->regmap、add、0x34);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

添加= 0x94;//HBR 1.62G bps

regmap_write (pdata->regmap、add、0x20);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

ADD = 0x0d;//PLL 启用

regmap_write (pdata->regmap、add、0x01);

msleep(10);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

msleep(10);

ADD = 0x0A;//训练模式应为0x01

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

添加= 0x95;//

regmap_write (pdata->regmap、add、0x00);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

ADD = 0x96;//自动训练

regmap_write (pdata->regmap、add、0x02);

msleep(5);

regmap_write (pdata->regmap、add、0x0A);

msleep(200 );

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

msleep(10);

/*配置视频参数*/

TI_SN_BRIDGE_SET_VIDEO_TIMING (pdata);

ADD = 0x5B;// 24bpp

regmap_write (pdata->regmap、add、0x00);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

添加= 0x3C;//色条

regmap_write (pdata->regmap、add、0x10);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

msleep(10);

ADD = 0x96;//训练模式应为0x01

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

添加= 0x5A;// cn

regmap_write (pdata->regmap、add、0xFC);

regmap_read (pdata->regmap、add、&read_val);

drm_error ("IIC 回读添加%x val %x\n"、添加、read_val);

msleep(10);

您好!

您是否已使用 DSI86电子表格计算其寄存器编程值? 对于 DSI86配置、请使用此 e2e 博文中的电子表格、 https://e2e.ti.com/support/interface-group/interface/f/interface-forum/945404/faq-sn65dsi86-how-do-i-programming-the-sn65dsi86-registers

查看 EDID、垂直前沿值(EDID 寄存器地址0x40和0x41)对于 DSI86寄存器空间来说似乎太大、这意味着 DSI86可能无法支持此特定面板。

我随附了带和不带 ASSR 示例的色条、您能看一下其中任何一个示例是否有效吗?

3513.2DP_4DSI_RBR_800x600_DPR.zip Color_Bar

2DP_4DSI_RBR_800x600_DSP Color_Bar_ASSR.zip

谢谢

大卫

您好, David,

是的、我们已经使用 DSI86电子表格计算了它的寄存器编程值。

下表是我们从面板 EDID 获得的 eDP/DP 面板时序。

| 73、51 | DCLK |

| 1280 | H 有效 |

| 117 | H 消隐 |

| 720 | V 有效 |

| 157 | V 消隐 |

| 53 | 水平前沿 |

| 32 | 水平同步宽度 |

| 32 | 水平后沿 |

| 63 | V 前沿 |

| 10 | 垂直同步宽度 |

| 84 | V 后沿 |

SN65DSI86 寄存器设置与 EDID 相同。

[6.23385][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加20 val 0

[6.2334316][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加21 val 5

[6.234334][DRM:ti_SN_BRIDGE_ENABLE]* ERROR*肖恩桥接设置视频 hdisplay 1280

[6.237625][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加24 val d0

[6.238119][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加25 val 2

[6.238141][DRM:ti_SN_BRIDGE_ENABLE]* ERROR*肖恩桥接设置视频 vdisplay 720

[6.238906][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加2c val 20

[6.238924][DRM:ti_SN_BRIDGE_ENABLE]* ERROR*肖恩桥接设置视频结束启动32

[6.239681][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加2D val 80

[6.239701][DRM:ti_SN_BRIDGE_ENABLE]*错误*肖恩桥接设置视频 HSYNC_POLARITY 128

[ 6.240460][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 读回添加30 val a

[6.240481][DRM:ti_SN_BRIDGE_ENABLE]*错误*肖恩桥接设置视频同步结束-开始10

[6.242613][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 读回添加31 val 80

[6.242641][DRM:ti_SN_BRIDGE_ENABLE]* ERROR*肖恩桥接设置视频 vsync_POLARITY 128

[6.243402][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加34 val 20

[6.243419][DRM:ti_SN_BRIDGE_ENABLE]*错误*肖恩桥接设置视频总计-结束32

[6.244174][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加36 val 54

[6.244193][DRM:ti_SN_BRIDGE_ENABLE]*错误*肖恩桥接设置视频 vtotal -结束84

[6.245838][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加38 val 35

[6.245863][DRM:ti_SN_BRIDGE_ENABLE]* ERROR*肖恩桥接设置视频 hstart - hdisplay 53

[6.247003][DRM:ti_SN_BRIDGE_ENABLE]* ERROR* IIC 回读添加3a val 3f

[6.247023][DRM:ti_SN_BRIDGE_ENABLE]* ERROR*肖恩桥接设置视频 vstart - vdisplay 63

此致

艾米莉

您好!

HPD I/O 单元具有一个内部60-kΩ 下拉电阻器。 HPD 引脚需要一个1%串联外部51-kΩ 电阻、如图6所示。 根据 VESA 嵌入式 DisplayPort 标准、对于 DisplayPort 发送器、可以选择使用 HPD。 如果系统设计人员选择不使用 HPD、则软件必须通过设置 HPD_DISABLE 位来禁用 HPD。

对于 DP AUX、您需要在 AUXP 具有100k 下拉电阻接地、需要在 AUXN 具有100k 上拉电阻连接 DP_PWR。

DP 不支持 ASSR、因此您要通过10k 电阻器将 TEST2引脚拉至1.8V、并使用 寄存器0x5A 中的标准 DP 扰频器种子

对于 eDP、AUX 上的上拉/下拉是可选的、具体取决于 eDP 受电方要求。 如果 eDP 支持 ASSR、则使用 替代扰码器种子复位

您是否能够使用我提供的两个示例对 DSI86进行编程、看看它们是否起作用?

谢谢

大卫

尊敬的 David:

对于 DP 面板、显示供应商建议我们 在 AUX_P 上添加一个1MΩ Ω 上拉电阻器、在 AUX_N 上添加1MΩ Ω 下拉电阻器、这与 TI 的要求相冲突。 AUX 通信成功、但链路训练失败。 我们不知道链路训练为什么失败。

当将面板配置更改为 eDP 接口,Ω 并使 TEST2保持接地、并且 AUX 通道上没有上拉和下拉电阻器时、链路训练成功。 由于 eDP 面板不支持 ASSR、因此无法显示。 我们正在等待可以支持供应商 ASSR 的新配置面板。

我没有尝试您给我的示例、因为某些寄存器设置与我们的设计不同。 例如、通道配置和极性需要更改。

您好!

大多数 DP 监视器不 支持 ASSR。 在这种情况下、需要通过设置 ASSR_control 读取/写入来禁用 DSI86的 ASSR、而不是只读。 实现 ASSR_CONTROL 读取/写入的第一步是确保在 EN 引脚的上升沿对 TEST2引脚进行高电平采样。 建议通过一个1k 至10k 电阻器将 TEST2引脚拉至1.8V。 一旦 TEST2为高电平、必须执行以下步骤:

1.将0x07写入寄存器0xFF。 此时将选择"Page 7"。

2.将0x01写入寄存器0x16。 这将使 ASSR_control 成为读取/写入。

3.将0x00写入寄存器0xFF。 这将选择"Page 0"。

4.将0写入寄存器0x5A 的1:0位。 这会从 ASSR 更改为标准 DP。

您是否完成了第1步到第4步?

谢谢

大卫

您好, David,

是的、TEST2已通过4.7kΩ 电阻器上拉至1.8V、并且寄存器已配置为 FLW、但 DP 训练失败。

regmap_write (pdata->regmap、0xff、0x07);

regmap_write (pdata->regmap、0x16、0x01);

regmap_write (pdata->regmap、0xff、0x00);

ADD = 0x5A;//F4 POLOR 增强帧和 ASSR

regmap_write (pdata->regmap、add、0xF4);

此致

艾米莉