工具与软件:

您好!

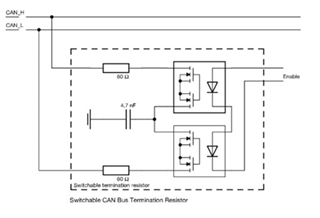

我们拥有一个系统、其中 LVDS 驱动器输出信号的 VCM = 2.1V、VID = 1.1V (当通过2.5米电缆连接到用作参考时钟的1 MHz 上的单个120欧姆输入端接 LVDS 接收器时、每条 LVDS 线路的摆幅均为2.1V 至2.65V (相对于接地)。 这意味着 Vcm 超出了标准 LVDS 接收器的(2.4V - VID/2) LVDS 输入要求。 我们是否可以使用 DS91M125将该非标准 LVDS 信号(参考时钟)分配到4个不同的模块、方法是使用2.5米电缆(Zo = 120欧姆、屏蔽双绞线)将每个模块连接到 DS91M125、并在其输入端具有120欧姆端接的标准 LVDS 接收器? 现有配置将该 LVDS 驱动器输出并联到4个单独的模块、每个模块都有2.5米电缆、该电缆为具有120欧姆端接电阻的 LVDS 接收器馈电。 我们怀疑4个 LVDS 接收器通过电缆并联到单个驱动器不是稳定的设计、尽管原始设计人员似乎包含了具有更高输出的 LVDS 驱动器来驱动30欧姆的有效负载。 是否有具有单路 M-LVDS 接收器(最好采用 SOT23封装)的芯片?

如果 DS91M125的其中一个驱动器输出(反相或同相、或两者)保持开路、而相应的使能(DE)引脚为高电平有效、会发生什么情况? 是否会在启用并正确端接其他三个驱动器输出时引起任何问题/噪声?

谢谢你。