请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TVP5150AM1-TVP EP 工具与软件:

尊敬的 TI 团队:

我们在设计中使用两个 TVP5150AM1PBSR 将 NTSC 数据转换为数字数据。

我们的板具有两个相同的视频解码器部分、这两个部分同时加电并且它们接收从单个视频源提供的通用视频输入。

上电时、这两个器件都会收到复位信号并通过两个单独的 FPGA 器件同时进行配置。

我们观察到、复位释放和视频锁定中断到达 VBLNK 引脚之间的间隔随每个下电上电的不同而变化、并且电路板上的两个部分也不同。

是否预计会出现此行为、或者我们是否需要在解码器 IC 上配置某些内容来解决此问题?

用于配置解码器的 I2C 事务如下

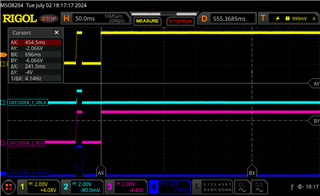

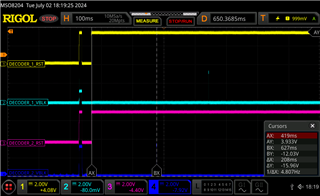

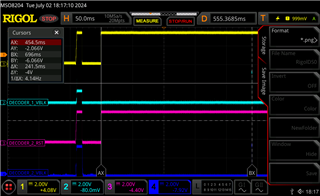

此外、我还附上了示波器截图、供您参考。 请查看并为该问题建议解决方案。

注意:

CH1 Decoder_1_Reset

通道2 DECC_1_VBLK

通道3 Decoder_2_Reset

通道4 DECODER_2_VBLK

此致

Keshav