工具与软件:

您好、先生、

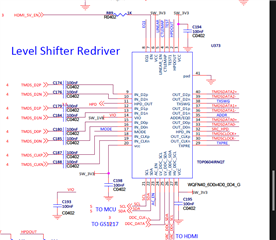

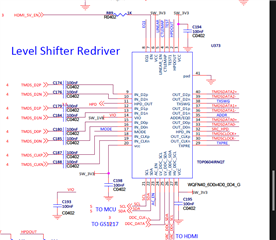

我的客户在其视频主机应用中使用 TDP0604。 在他们的测试中、他们修改了 GPIO 设置以在高分辨率(4K 60Hz)下解决视频刷写问题。

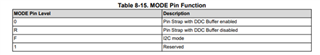

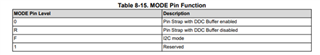

在他们的实验中、他们拉高了模式引脚、问题将得到解决。 但在数据表中没有关于 MODE = 1的定义。 在 TDP0604处、MODE = 1是否有任何间隔功能、或者是否可以设置 MODE = 1?g

此致、

Gary Teng

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、先生、

我的客户在其视频主机应用中使用 TDP0604。 在他们的测试中、他们修改了 GPIO 设置以在高分辨率(4K 60Hz)下解决视频刷写问题。

在他们的实验中、他们拉高了模式引脚、问题将得到解决。 但在数据表中没有关于 MODE = 1的定义。 在 TDP0604处、MODE = 1是否有任何间隔功能、或者是否可以设置 MODE = 1?g

此致、

Gary Teng

Gary

它们是在引脚搭接模式还是 I2C 模式下使用 TDP0604? 如果 MODE 引脚悬空、原理图本身显示 TDP0604处于 I2C 模式。 如果是这种情况、那么您能否共享 TDP0604的寄存器转储? 如果他们将模式引脚更改为1、那么您处于引脚搭接模式、我们必须查看看起来不正确的引脚搭接模式配置。

1.LINEAR_EN 需要通过1k 电阻拉至 GND、以便将 TDP0604设置为限幅模式

AC_EN 需要拉至 GND 以实现直流耦合输出

3. TXSWING 需要通过1k 电阻拉至 GND、以设置默认1000mVpp 振幅

4.将 TX_PRE 保持悬空状态以实现0dB 去加重

5.通过一个1k 的电阻器将 CTLEMAP_SEL 拉至高电平

6. CFG0和1需要通过1k 电阻拉至 GND

谢谢

David

您好!

在引脚搭接模式下、您是否可以进行以下修改? 您是否还完成了 HDMI2.0合规性测试?

1.LINEAR_EN 需要通过1k 电阻拉至 GND、以便将 TDP0604设置为限幅模式

AC_EN 需要拉至 GND 以实现直流耦合输出

3. TXSWING 需要通过1k 电阻拉至 GND、以设置默认1000mVpp 振幅

4.将 TX_PRE 保持悬空状态以实现0dB 去加重

5.通过一个1k 的电阻器将 CTLEMAP_SEL 拉至高电平

6. CFG0和1需要通过1k 电阻拉至 GND

谢谢

David