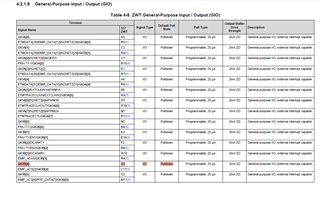

Other Parts Discussed in Thread: HALCOGEN, RM46L852, DP83640

主题中讨论的其他器件:HALCOGEN、 RM46L852、

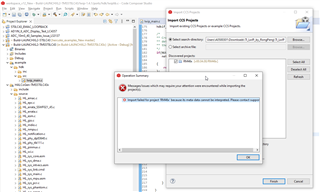

工具与软件:

各位专家、您好!

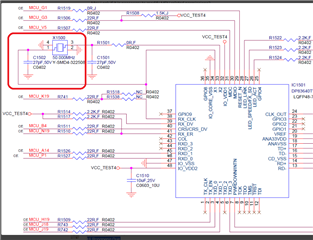

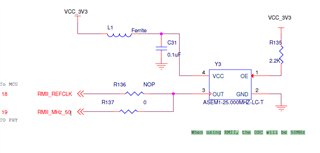

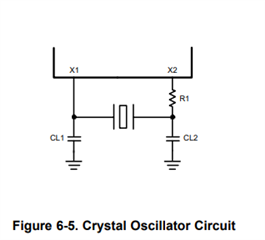

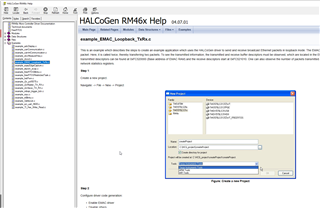

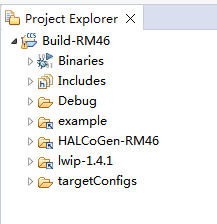

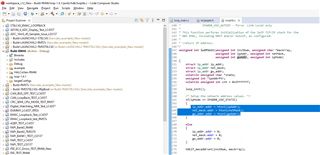

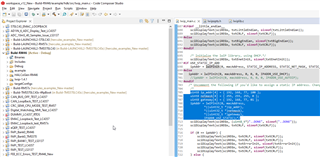

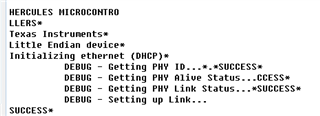

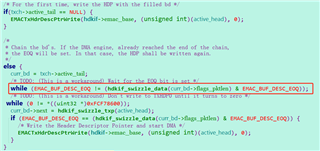

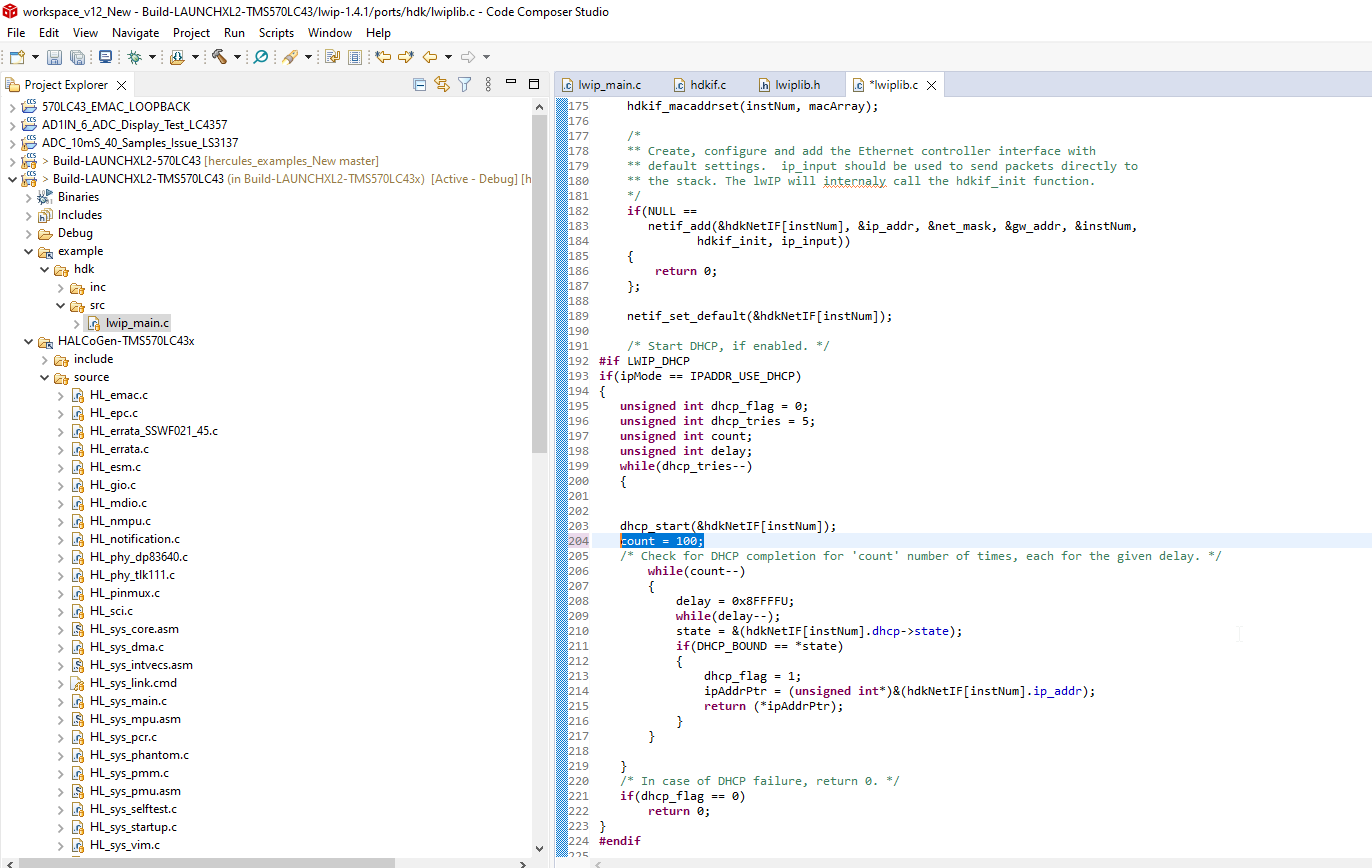

我正在尝试通过使用 RMII 和 RM46L852 MCU 以及使用 FreeRTOS 和 UDP 堆栈的定制开发板实现以太网通信。 我正在使用 HALCoGen 生成的驱动程序代码执行硬件初始化。 我正在按照确切顺序进行的初始化包括:

1.启用中断

2.初始化 SCI 和 GIO

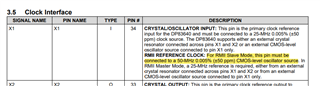

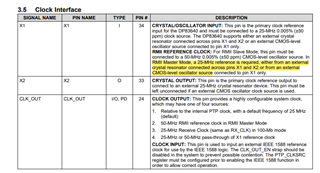

3.以 CPU 时钟频率初始化 MDIO 作为输入频率、以2.5MHz 作为输出频率

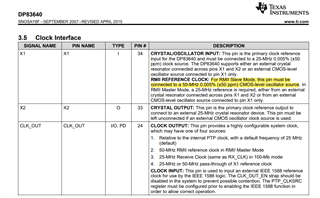

4.使用 EMAC_0_BASE、EMAC_PHYBASE 和 MDIO_0_BASE 的 EMACLinkSetup 执行 DP83640 PHY 链路设置。

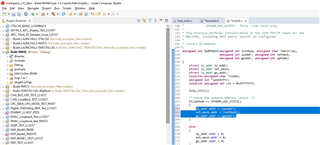

5.使用 DP83640模块上的引脚29 (置位然后取消置位)执行 PHY 复位。

6. EMACInit 使用 EMAC_0_CTRL_BASE 和 EMAC_0_BASE。

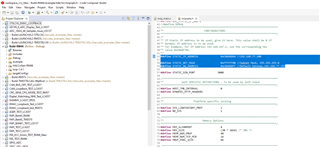

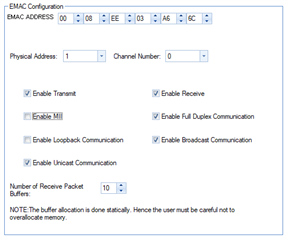

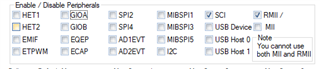

此处、EMAC_0_CTRL_BASE、EMAC_0_BASE 等都是 HALCoGen 生成的常量。 如果可能有用、我还将在 HALCoGen 中附加 EMAC 配置以及 PINMUX:

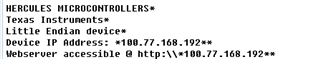

之后我使用 FreeRTOS_IPInit()函数初始化 TCP 加 UDP 堆栈、并启动以太网任务。

我想确认初始化步骤的有效性、或者如果我缺少一些配置、因为这不起作用。 当我尝试使用调度程序时、套接字的内存分配失败、我唯一能够启动以太网任务的方法是手动将其作为一个函数调用、这让我觉得硬件配置可能是个问题。

DP83640是否未正确设置? 我这边的任何其他信息是否可以帮助您找到问题所在?

请说明、是否有使用 DP83640和 RM46L852 MCU 的 MDIO 和 RMII 测试网络连接的示例项目?

谢谢!

- Karan