主题中讨论的其他器件:HD3SS3220、 DS160PR421、 SN75LVPE5412

工具与软件:

这些是我在此类电路中的第一步、我非常感谢一位专家的意见:

大标题:

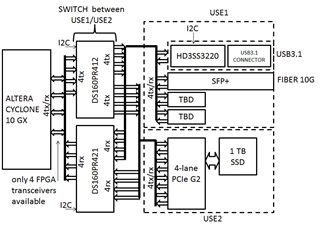

我正在使用 Altera Cyclone 10 GX FPGA、需要将4个 FPGA 收发器(能够支持12.5Gbps)多路复用到两个需要动态选择的应用中:

>在 Use1中,四个收发器支持短距离连接到固态磁盘,使用4通道 PCIe Gen2接口,速度为5Gbps。

>在 Use2中,将分配四个收发器来支持一个 USB3.1端口、一个 SFP+ 10G 光纤链路和两个板间链路(仍待定)。 对于 USB 3.1前端、我选择了 TI 的 HD3SS3220 10Gbps USB 3.1 Type-C 2:1多路复用器(带 DRP 控制器)。

现在、我的问题是:

至于在 HD3SS3220和 FPGA 之间放置的四路2:1多路复用器/多路信号分离器、我已计划使用 TI 的 DS160PR412/421对在4通道 PCIe (使用1)与 USB 3.1 + SFP++ 2TBD (使用2)之间进行切换和转接驱动。 由于 DS160PR412/421和 HD3SS3220增益和 EQ 行为可通过 I2C 动态编程、因此我假设可使用上述设置实现此目的。

这是对的、我遗漏了一些基本的东西还是犯了大错误?

非常感谢

Guillermo.