工具与软件:

您好!

我们 在设计中使用了上述多路信号分离器、因此根据选择线、我们可以将端口 A 用作 USB3.1、将端口 B 用作 PCIe 信号。 我们将从 SOC 到该多路信号分离器的 SERDES 2通道(TX0、1和 RX0、1)连接为输入信号。 此处 SERDES 接口信号在 SOC 中进行引脚多路复用、因此我们可以将这些引脚配置为 USB 或 PCIe。 提供了 SNAP 作为单通道的参考。

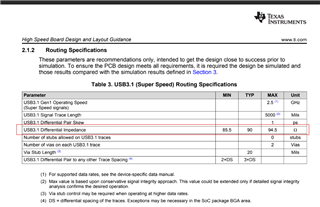

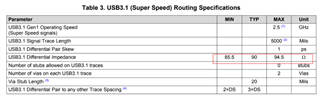

我在这里的问题是、我们如何在 PCB 中对这2个通道(从 SOC 到多路信号分离器)进行布线、因为这两个接口具有不同的布线阻抗、如 PCIe (85 Ω)和 USB3.1 (90 Ω)? 请建议如何在 PCB 上路由这些信号?