Other Parts Discussed in Thread: TPD4E02B04

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1417578/tpd4e02b04-voltage

器件型号:TPD4E02B04Thread 中讨论的其他零件: Strike

工具与软件:

Dears、

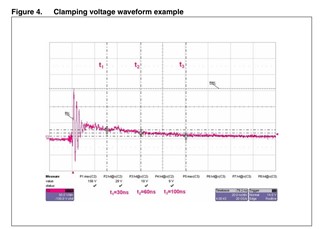

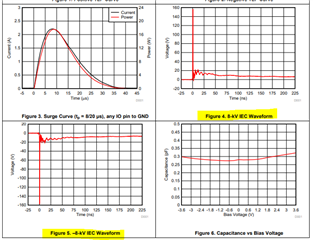

TI 的 ESD 产品 TPD4E02B04是在 ESD 的两端使用接触静电时的实际嵌入式电压波形图。 问题是、为什么 ESD 两端的嵌入电压从正160V 变为负70V? ESD 两端在 t1到 t3时刻的插入电压下降的原因是、在 ESD 将静电释放到 GND 后、插入电压会下降。

请帮助检查一下。

谢谢