主题中讨论的其他器件: DP83640

工具与软件:

您好!

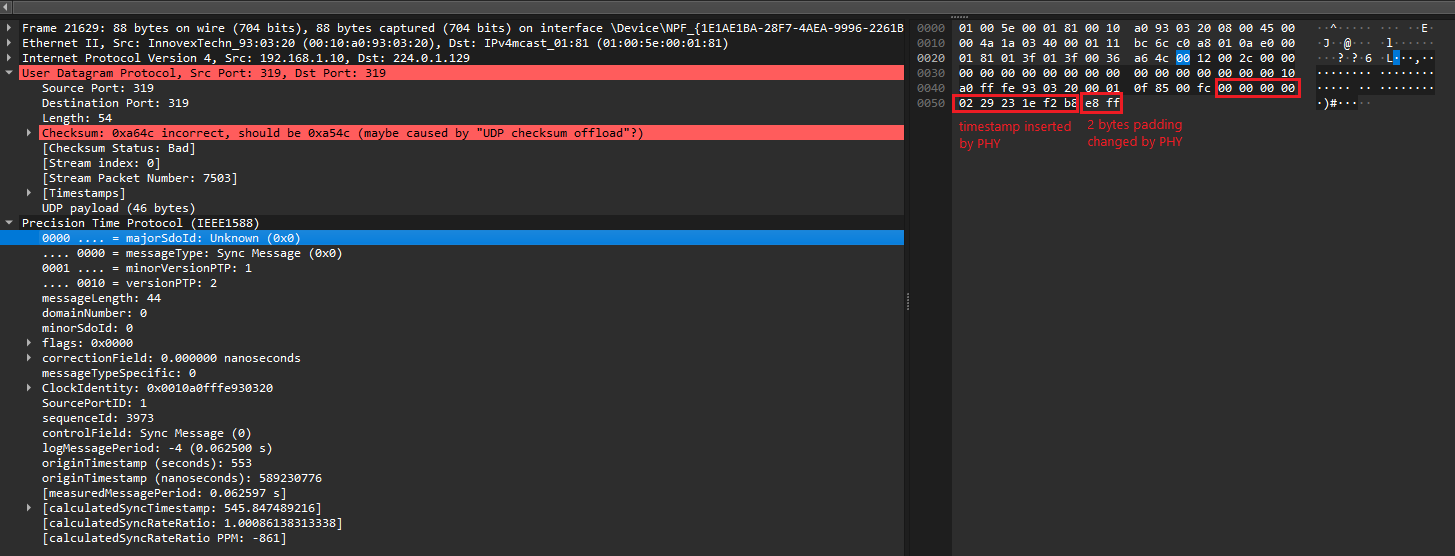

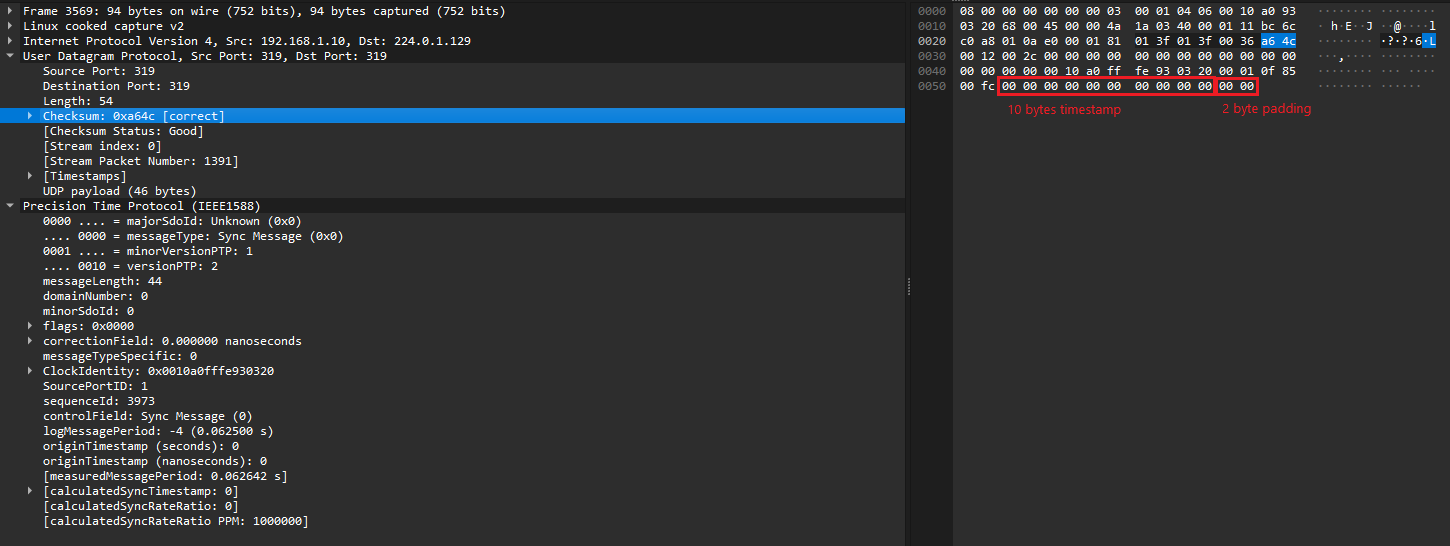

我将 DP83630芯片的 Linux 系统用于 PTP。 我注意到、偶尔、如果是单步同步数据包(DP83630插入正确的时间戳并交替2个填充字节以获得正确的校验和)、操作的填充字节会导致 UDP 校验和仍然错误。 错误的 UDP 校验和被1除、例如0x1538而不是0x1539。

您是否熟悉此类行为?

需要注意的是、我使用的 DP83630 EVK 中的芯片仍然有 National Semiconductor 标识。

谢谢!

Alexey。