工具与软件:

您好、TI:

如果客户将我们的芯片与 TI941+TI948一起使用、则会出现一些 ICS 抖动屏幕的具体现象:

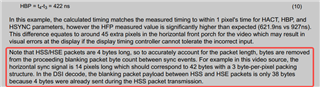

屏幕定时:像素 clk=HPSW=1920 147.46MHz、h_act=1920、HFP=64、HBP=32、HSW=32、 V_ACT=1080、VFP=104、VBP=6、VFP=6

DSI 配置:1个时钟通道+4个数据通道、DSI 445MHz、数据速率=890MBps

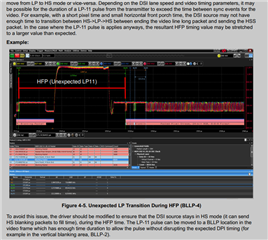

1000个客户端中大约有一个或两个会抖动。 DSI 波形测量完成后发现、正常芯片在一帧内进入 LP 状态12次、异常芯片会随机进入 LP 状态

11或12次。 DSI 数据速率增加到905MBps 后、还可以正常显示异常 IC。

现在、TI 需要确认以下问题:

1: 导致以上抖动屏幕的原因是什么?

2:当 DSI 在一帧中11次或12次进入 LP 状态以进行 TI941解析时序时、有什么不同?

3: TI941对于 DSI 时序的具体要求是什么? 例如、DSI 源屏幕的 DSI 时钟和计时有哪些具体限制? 如何配置它以确保正常显示