Other Parts Discussed in Thread: DS89C21

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1420949/ds89c21-ds89c21

器件型号:DS89C21工具与软件:

您好!

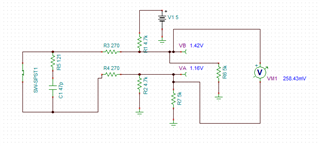

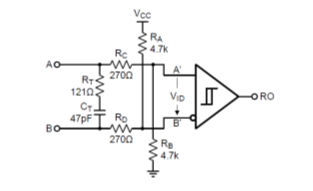

我想使用反向极化实现可降低功耗的交流端接、以便在输入发生高阻抗故障或短路时确保低输出、如以下原理图所示。

您能否确认极化电路将具有 DS89C21接收器输入阻抗的正确行为(输入高电平或短路时输出低)? 而且它不会干扰通信的操作模式,因为它是一个低速控制应用(最大30kHz),点对点距离最大50cm 到1m。

提前感谢您的帮助、我无法对其进行仿真(仅可使用 IBIS 模型)。

此致

Pierre