工具与软件:

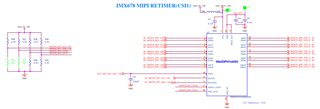

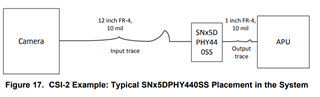

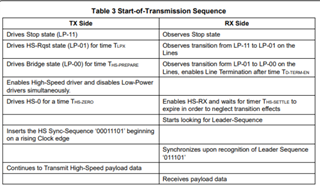

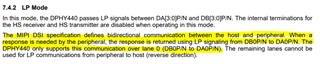

我们目前正在开发 PTZ 摄像头监控系统、并使用 SN65DPHY440SSRHR 重定时器来延长 MIPI HS 信号长度。

当前问题是:我们遇到了随机的瞬时卡住问题。

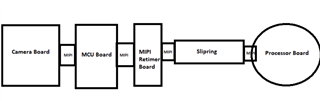

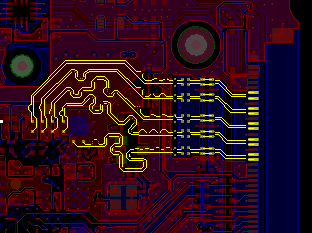

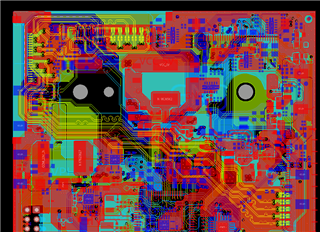

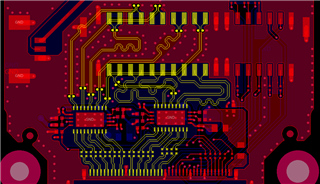

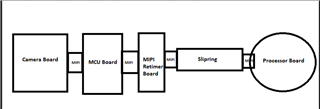

MIPI 总长度约为650米、信号通过各种电路板从摄像头传输到处理器、请参阅下图。

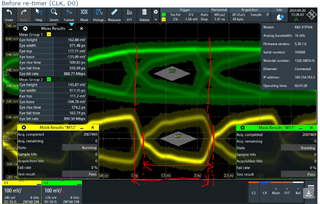

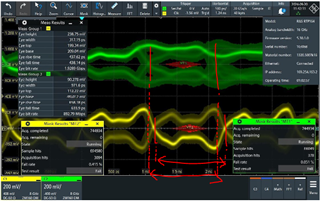

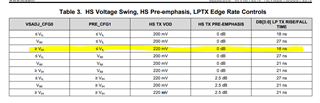

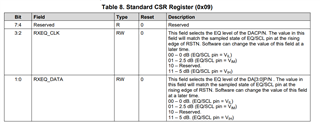

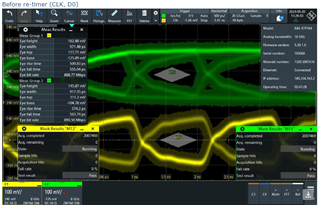

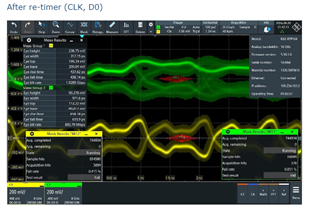

我们还观察到、眼图在 MIPI 重定时器 IC 之前和之后都出现故障。 您能否介绍重定时器 IC、并就我们为了更好地调优 MIPI 信号而可以实施的潜在变化提供指导? 我们已采用 MIPI 重定时器的默认硬件配置进行了测试。

重定时器之前(CLK、D0)

另外、还观察到重定时器之后的 MIPI 时钟数据速率从原来的890Mbps 变为1.9Mbps。