Thread 中讨论的其他器件: SN65DSI84

工具与软件:

嗨团队、

请澄清以下问题:

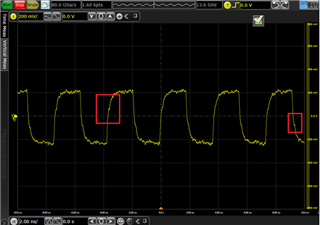

1.我们看到 DSI CLK 波形的上升沿和下降沿都有一些毛刺脉冲(如下图红框中所示)。 SN65DSI84-Q1中是否有滤波器或其他相关电路可以消除此干扰的影响?

这些干扰是否会影响 SN65DSI84-Q1的采样?

2.我们在 TI 官网上看到 SN65DSI84的仿真波形、但是它的封装跟 SN65DSI84-Q1不同(不确定还有其他的区别)。

我能否使用以下链接中 SN65DSI84的仿真模型来仿真 SN65DSI84-Q1的信号完整性?

https://www.ti.com.cn/product/cn/SN65DSI84#design-tools-simulation