Other Parts Discussed in Thread: TCA9517-Q1

工具与软件:

您好、TI 专家

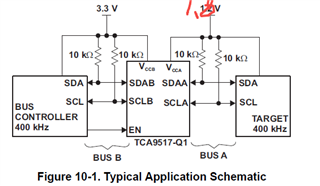

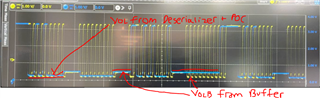

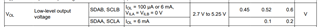

我们使用与图中所示结构类似的结构来设计具有3.3V 电压的 MCU、该 MCU 通过 LEVELSHIFT 转换为1.8V 电平。 偶尔会发生 MCU I2C 卡死区的情况、测试 BUS-B (SCL 为高电平3.3V、SDA 为低电平0.5V)。BUS-A 的 SCL 为1.8V 的高电平、而 SDA 为约0V 的低电平。

(1)我是否可以询问哪些情况会导致这种情况?

(2)我们试图关闭和打开 VCCA 的电源、但总线仍然冻结。 VCCA 断电后、总线 B 的 SDA 是否仍能输出0.5V 的低电平?

谢谢你