主题中讨论的其他器件: USB-2-MDIO

工具与软件:

您好!

我们在 Spartan-7 FPGA 中使用具有软 MAC 的 DP83826I、并遇到零星的数据包接收错误。 MAC 有时仅接收551字节数据包的第一部分。 完整接收前一个和后续的数据包。 我们只会在接收方向上看到错误 并且仅当我们同时传输流量时 (每3ms 192字节数据包)。 如果我们停止传输、则所有数据包都将被完整接收。

RX 流量来自通过板对板连接的独立电路板上的嵌入式交换机。

我们认为这种流量是好的(请参阅下面的详细信息)、但是当 PHY 将截断的数据包转发到 MAC 时(这显然会产生 CRC 错误)、PHY 不会报告任何错误、低链路质量或类似情况。

我们忽略了没有正确的解释来解释 PHY 中的此行为吗?

更多详细信息:

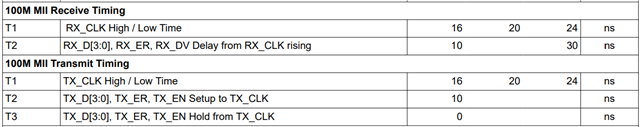

PHY 是 MII 主模式、我们使用固定链路100Mbit 全双工模式。

在 MDI 侧、有一个板对板连接、连接到带有嵌入式漫威开关的主板(mv88e6290)。

┌────────────────μ A ┐ ┌────────────────────μ A ┐μ A

│CPU <->开关│<- Board2Board ->│PHY <->具有 MAC 的 FPGA│

└────────────────μ A ┘Ω 连接器 └────────────────────Ω ┘μ A

我们的理解是、RX_DV 信号显示了25MHz MII 接口上数据有效时的周期、从检查该信号置为有效时的长度可以看出 PHY 向 MAC 发送的数据包过短。 发生错误时发送的字节数不是恒定的(我们已经看到从120个字节到500个字节的任何内容)。

我们一直在检查 PHY 状态寄存器、没有发现 PHY 报告错误的迹象:

-良好的链路质量,即使发生错误: MSE_Val (reg 0218h ):小于0030h (48)。

-无接收错误(RX_ER 线路从未被置为有效、RECR = 0、PHYSTS 中的 ReceiveErrorLatch 为0)

-链路质量、状态等无变化(MISR1=0)

-无远程故障,解码器锁激活,检测到信号,没有错误载波发生(PHYSTS=0605)

事实上、该错误仅在同时传输时发生、我们认为可能存在噪声/串扰问题、但随后我们会预期收到一些完整的数据包、其中会出现位错误(在 MAC 中报告为 CRC 错误)。 我们还没有看到、只有短数据包位于 RX 方向。

另外、如果在 PHY 的 MDI 侧接收符号时出现错误、我们预计会看到链路错误或接收错误。 这两种情况都看不到。

由于我们无法轻松地直接分析 Board2Board 连接上的信号、因此我们使用一个小的调试接口板来代替 FPGA 板进行连接、使我们可以在 PC 上的软件中运行数据、从而模拟 FPGA 功能:

┌────────────────μ A ┐ ┌─────────────────μ A ┐ ┌────────────────μ A ┐μ A

│CPU <->开关│<- Board2Board ->│接口板│<- Cat5e ->│PC w/FPGA sim│Ω

└────────────────μ A ┘Ω 连接器 │Ω、 带 RJ-45 │ └──────────────── ┘μ A

└─────────────────μ A ┘μ A

使用此设置时我们没有看到任何错误(FPGA sim 还会仿真 TX 流量)、因此我们认为 CPU 板上的嵌入式开关发送的数据是可以的。

侧边注释:

奇怪的是、当没有以太网流量流经 PHY 时、RX FIFO 溢出(RCSR = 0x41)被置为有效。 当我们启用流量(无论方向是 RX 还是 TX)时、溢出状态会在短时间后取消置位。 溢出断言似乎与我们看到的接收错误没有链接、但我们不确定该断言的作用、因为我们的 PHY 是 MII 主器件。

在主模式下、什么会使 PHY 使 RX FIFO 溢出生效?

此致、

Mikael