工具与软件:

SN65DSI86使用什么标准来确定和报告链路时钟和流时钟是异步还是同步?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

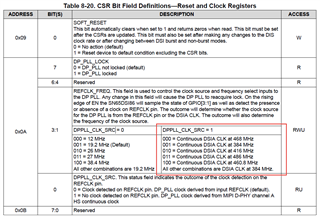

感谢您的澄清。 我们遇到的情况是 REFCLK_freq 配置为486Mhz 的 DSIA CLK、并且寄存器0x0A 按预期报告(0x0A = 0x87)。

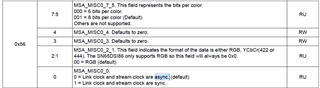

但是、寄存器0x56报告0x20、表示"ASYNC"。 鉴于为 DSIA CLK 配置了基准时钟、我们期望这会报告"Sync"。 显示端口 MSA 数据也报告"ASYNC"。

对于这种意外行为、您有什么建议或可能的解释吗?

尊敬的 Augusto:

查看 Verilog 文件后、我发现流是异步的原因。

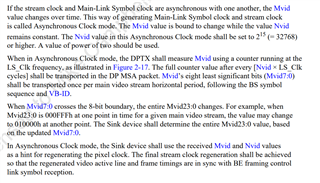

根据 DP 规范、我们知道如果链路时钟和流时钟来自同一源、则流是同步的。 在同步流中、Nvid 和 Mvid 的比率是一些基于所使用的数据速率的硬编码值。

在异步流中、Nvid 保持为恒定值。在每个时钟周期中、一个计数器都会递增。 实现方式如下。

这种异步 Mvid 和 Nvid 计算可用于为同步流和同步流生成 Mvid 和 Nvid 值。 在我们的设计中、我们为异步和同步流实现了异步 Mvid 和 Nvid 计算。 这就是使用此器件时、MSA 位始终会异步读取的原因。

有趣的是、我将与一位系统工程师讨论这一部件、明天我将与您联系。 我同意这是意外行为。 [报价]我对这一发言引起的任何混淆表示歉意。 当时我并不了解我们的设计。

此致!

Vishesh Pithadiya