工具与软件:

您好!

我在几周前打开了这个案例、但不幸的是、我无法及时进行测量、且案例在几天后关闭。

最初的用例是 DP83867ERGZ-S-EVM:RFSoC (Ultrascale+) DP83867ERGZ-S-EVM 链路接通但无流量(Ping)

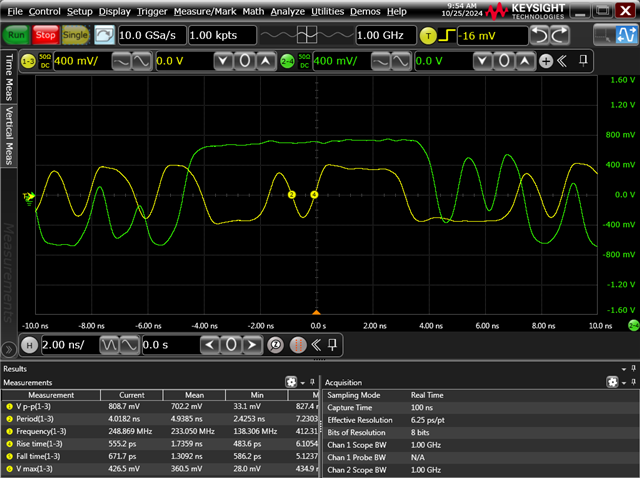

我最终进行了测量、但示波器具有1GHz BW 的限制、而且信号非常有限。

在此捕获图中、黄色对应于评估板 DP83867ERGZ-S-EVM (SO_P-SO_N)的差分输出。 绿色输出是 FPGA (PS-GTR3、GEM3)的输出。

评估板的振幅似乎可以接受、在100欧姆的差分阻抗上大约800mV。 RF-SoC 的振幅似乎正常、差分 P-P 振幅为1500mv aprox。

寄存器0x0037保持0值、此值表示 SGMII 自动协商未完成、

置于 U-boot 中

ZynqMP> mii write 0x00 0x0D 0x001F ZynqMP> mii write 0x00 0x0E 0x0037 ZynqMP> mii write 0x00 0x0D 0x401F ZynqMP> mii read 0x00 0x0E 0000

并在 Linux 中运行

Reg: 0x0000 Value: 0x1140 Reg: 0x0001 Value: 0x796D Reg: 0x0002 Value: 0x2000 Reg: 0x0003 Value: 0xA231 Reg: 0x0004 Value: 0x09E1 Reg: 0x0005 Value: 0xCDE1 Reg: 0x0006 Value: 0x006F Reg: 0x0007 Value: 0x2001 Reg: 0x0008 Value: 0x4006 Reg: 0x0009 Value: 0x0300 Reg: 0x000A Value: 0x3C00 Reg: 0x000D Value: 0x401F Reg: 0x000E Value: 0x1111 Reg: 0x000F Value: 0x3000 Reg: 0x0010 Value: 0x5848 Reg: 0x0011 Value: 0xAC02 Reg: 0x0012 Value: 0x0000 Reg: 0x0013 Value: 0x1C02 Reg: 0x0014 Value: 0x2BC7 Reg: 0x0015 Value: 0x0000 Reg: 0x0016 Value: 0x0000 Reg: 0x0017 Value: 0x0040 Reg: 0x0018 Value: 0x6150 Reg: 0x0019 Value: 0x4440 Reg: 0x001A Value: 0x0002 Reg: 0x001E Value: 0x0202 Reg: 0x001F Value: 0x0000 Reg: 0x0031 Value: 0x1111 Reg: 0x0032 Value: 0x00D3 Reg: 0x0033 Value: 0x0000 Reg: 0x0037 Value: 0x0000 Reg: 0x0043 Value: 0x07A0 Reg: 0x006E Value: 0x8820 Reg: 0x006F Value: 0x0110 Reg: 0x0086 Value: 0x0057 Reg: 0x00C6 Value: 0x0000 Reg: 0x00D3 Value: 0x0000 Reg: 0x00FE Value: 0xE721 Reg: 0x0134 Value: 0x1000 Reg: 0x0135 Value: 0x0000 Reg: 0x016F Value: 0x0015 Reg: 0x0170 Value: 0x0C12 Reg: 0x0172 Value: 0x0000 Reg: 0x01D5 Value: 0xF500

来自 PHY 的自动协商正常、来自 PHY 的所有内容似乎正常

root@sgmii:~# dmesg | grep macb [ 2.130847] macb ff0e0000.ethernet: Not enabling partial store and forward [ 2.147282] macb ff0e0000.ethernet eth0: Cadence GEM rev 0x50070106 at 0xff0e0000 irq 45 (00:0a:35:00:22:03) [ 7.663446] macb ff0e0000.ethernet eth0: PHY [ff0e0000.ethernet-ffffffff:00] driver [TI DP83867] (irq=POLL) [ 7.673253] macb ff0e0000.ethernet eth0: configuring for phy/sgmii link mode [ 7.685382] macb ff0e0000.ethernet: gem-ptp-timer ptp clock registered. [ 11.775311] macb ff0e0000.ethernet eth0: Link is Up - 1Gbps/Full - flow control tx

也许您能帮我找出为什么我无法通过 SGMII 在 GEM 和 PHY 之间获得链接和自动协商?

非常感谢。