工具与软件:

1: 外部 EEPROM 的芯片负载、如何处理引脚 en_SMB (E3)和 read_en_n (F13)?两者都是下拉的?

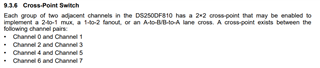

2: DS250DF810的交叉点如何,请提供 pciture

3:应用在 zqsfp+中的4通道上为100G、请提供 eeporm 文件。

4:设计中使用了两个芯片、引脚 cal_clk_in 分别使用晶体、引脚 cal_clk_out (E15) 不连接、这可以?

5:什么是价格和如何购买它在中国北京

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

1: 外部 EEPROM 的芯片负载、如何处理引脚 en_SMB (E3)和 read_en_n (F13)?两者都是下拉的?

2: DS250DF810的交叉点如何,请提供 pciture

3:应用在 zqsfp+中的4通道上为100G、请提供 eeporm 文件。

4:设计中使用了两个芯片、引脚 cal_clk_in 分别使用晶体、引脚 cal_clk_out (E15) 不连接、这可以?

5:什么是价格和如何购买它在中国北京

谢谢!

Drew

您好!

PCB 中的芯片在哪里? 它是否靠近控制器(CPU)或连接器(zqsfp+)? 如何处理 QUESTTON[/报价]我们通常看到重定时器放置在更靠近连接器的位置。 但是、这将取决于 CPU <->连接器之间的插入损耗大小以及 CPU 具有的均衡能力。 CPU <->重定时器之间的插入损耗必须在 CPU 的均衡能力范围内、这一点很重要。

此外、重定时器在 CTLE 指数0处具有高升压。 因此、请在 CPU <->重定时器和连接器<->之间保留至少3dB (假设您将使用光学模块)。 这将有助于避免过度均衡。

1:加载 EEPROM 后、引脚 ALL_DONE_n (D3)的槽为低电平?是的、这是正确的。

2:EEPROM 至少有多少容量?我建议使用1kB 或2kB EEPROM。

谢谢!

Drew

[/quote]