https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1436558/sn65dsi84-sn65dsi84

器件型号:SN65DSI84工具与软件:

团队成员、您好!

请注意、我们正处于需要"单 DSI 至双 LVDS 转换"的项目的设计阶段、并考虑选择 SN65DSI84。

我特此附上 SN65DSI84的原理图部分。

您能帮忙检查原理图吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1436558/sn65dsi84-sn65dsi84

器件型号:SN65DSI84工具与软件:

团队成员、您好!

请注意、我们正处于需要"单 DSI 至双 LVDS 转换"的项目的设计阶段、并考虑选择 SN65DSI84。

我特此附上 SN65DSI84的原理图部分。

您能帮忙检查原理图吗?

e2e.ti.com/.../SN65DSI84ZXHR_5F00_DSI_2D00_to_2D00_Dual_5F00_LVDS_5F00_Sch_5F00_for_5F00_review.pdf

尊敬的 Vishesh:

抱歉、我忘记上传相同的内容。

PFA 将上述的原理图部分用于审阅和反馈。

尊敬的 Yasar:

以下是我的评论:

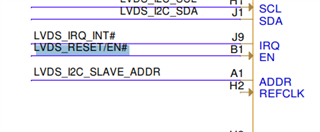

1) 1)在 EN 引脚上添加一个220nF 电容器、接地。 该 SI 可减慢边沿速度、并满足启动时序要求。

2) 2)建议使用 REF 时钟、因为这将提供更干净的时钟。

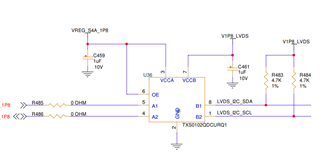

3) 3)为什么需要从1.8V 到1.8V 的电压转换器?

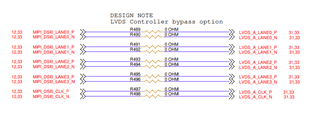

4)主链路路径上的电阻器应为0201封装。 请勿将我们的器件与另一条路径并联。 这将导致高速布线上出现主要反射。

尊敬的 Vishesh:

感谢您提供快速回顾反馈。

请在下方查看我的回复。

1) 1)在 EN 引脚上添加一个220nF 电容器、接地。 该 SI 可减慢边沿速度、并满足启动时序要求。

已添加。

2) 2)建议使用 REF 时钟、因为这将提供更干净的时钟。

我们是否真的需要使用外部参考时钟、因为数据表中显示为"可选"。

此外、我们还提供 D-PHY 差分时钟。

这2个时钟是否不同? 或者需要其中一个才能正常运行? 请澄清。

3) 3)为什么需要从1.8V 到1.8V 的电压转换器?

此处、一个1.8V 表示 SoC 电源轨、另一个是指 sn65dsi84电源轨。

在 SoC 完全供电/运行之前、我之所以进行隔离、是为了避免在 SoC 和 sn65dsi84之间产生信号流。

对于这种实施、您是否有任何顾虑?

4)主链路路径上的电阻器应为0201封装。 请勿将我们的器件与另一条路径并联。 这将导致高速布线上出现主要反射。

是的、这些旁路电阻器仅是0201封装。

我们将仅在没有 sn65dsi84芯片时组装这些电阻器、以在载板上获得 DSI 通道的直接映射。

我们是否真的需要使用外部参考时钟、因为数据表中显示为"可选"。

此外、我们还提供 D-PHY 差分时钟。

这2个时钟是否不同? 或者需要其中一个才能正常运行? 请澄清。

[报价]是的、也可以使用。 我建议使用 REF 时钟、因为时钟信号将更加干净、产生更好的 PLL 锁定。 根据我的经验、进入器件的 DSI 时钟往往会跨越电缆和布线、影响时钟的信号完整性、使 PLL 更难锁定。 使用外部时钟将缓解未来的 PLL 解锁问题。

如果使用 DSI 时钟在 DSI84的引脚处清除 DSI 时钟信号、则不存在问题。

[报价 userid="587390" url="~/support/interface-group/interface/f/interface-forum/1436558/sn65dsi84-sn65dsi84/5512394 #5512394"]此处、一个1.8V 表示 SoC 电源轨、另一个是指 sn65dsi84电源轨。

在 SoC 完全供电/运行之前、我之所以进行隔离、是为了避免在 SoC 和 sn65dsi84之间产生信号流。

对于这种实施、您是否有任何顾虑?

[报价]不用担心、只需好奇

我们将仅在没有 sn65dsi84芯片的情况下组装这些电阻器、以直接映射载波板上的 DSI 通道。

为减少反射、确保与这些旁路电阻器关联的任何残桩尽可能小。 请分享布局、以便在电路板准备就绪时进行审查。

尊敬的 Vishesh:

再次感谢您的支持。

我将分享更新后的原理图、并加入审核意见、以进行最终审核。

请提供帮助。