工具与软件:

您好!

我对 DP83825I 以太网 PHY 及其 RST_N 引脚的行为有疑问。

我们在设计中采用 DP83825I、其具有1.8V VDDIO。 但我们注意到、连接到 RST_N 引脚的复位信号的电压电平为2.2V-2.5V、而不是1.8V。

根据 DP83825I 数据表、RST_N 引脚应在与 VDDIO 相同的电压电平下运行。 您能否说明以下几点

- RST_N 引脚上的内部上拉电阻器是固定在3.3V 还是按照数据表中所述连接到 VDDIO?

- 如果连接至 VDDIO、是否在任何情况下会出现这种差异?

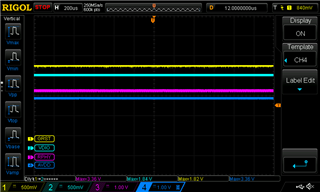

这种行为是我们设计中的一个关键问题、解决它对于确保正常运行至关重要。 为了帮助您了解这种情况、我附上了两个图:

- 一个显示连接了 PHY 后的行为。

- 另一幅图显示了 RST_N 引脚的信号断开时的行为。

非常感谢您就此事提出建议。

感谢您的支持!