Other Parts Discussed in Thread: DP83848C

工具与软件:

尊敬的 SIRs:

我正在使用 DP83848C 进行布局、我想知道 PFBOUT 23是否可以通过引脚18和37连接到 IC 下方的导线。

我有一个空间受限的设计、如果我可以将它们放在 IC 下、这将会有所帮助

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Gerwin:

感谢您提交查询、我很乐意提供帮助。 是的、您可以! 相关参考、请参阅 DP83848K-MAU-EK。 Altium 布局文件位于 Design Files 选项卡中。

请注意这是848 K 该器件型号的 PFBOUT 引脚为19、16和31、而不是23、18和 C 型号为37。

引脚通过一个过孔从顶层连接到底部(GND)层、并在此处全部连接在一起。

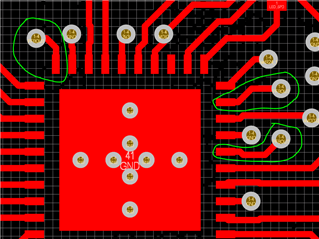

顶层

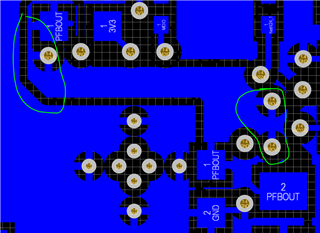

底层

此致、

Alvaro

你好、Alvaro、

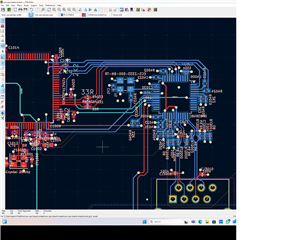

我把它弄出来了:

我正在使用一个6层板,因为一些其他的事情我需要添加,对于 RMII 信号长度匹配我有一些问题 TXD0 -TXD1 (约47mm)和 RXD 约37mm ref_clock 是37mm ,我路由信号在顶部和底部和一些低速信号在第4层,你认为长度差异与 TXD 和 RxD 真的很重要? 我读取到某个地方的差值可以是12mm (RXD0和 RXD1匹配、如 TXD0和 TXD1)