请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN65DP159 工具与软件:

大家好、团队成员:

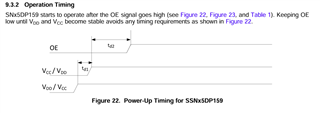

1.如果我有足够的时间将 OE 取消置位、直到所有 VCC 和 VDD 都稳定为止、那么在我的设计中、VCC 和 VDD 之间仍然会有1.4ms 的延迟、所以是否仍然需要考虑'TD1'的要求?

2. OE 保持无效的最长可接受时间是多少? (我使用 RC 滤波器进行延迟)

3.另外,两者之间1.4ms 的延迟是可以接受的吗?

4、VCC 在 VDD 之前的稳定性,或者反之,是否可以忽略?

下面附上了图像:

谢谢!

M Karthik