Thread 中讨论的其他器件:ALP

工具与软件:

背景:LT7911+TI941项目偶尔会出现闪光屏幕问题。

1.调试大屏幕项目的软件只能将 EDID 分辨率从1920X720->800X480改变。

小屏幕显示固定闪屏,当 LT7911D 开发板连接到其他 DSI 接收时,可以正常显示相同的固件。

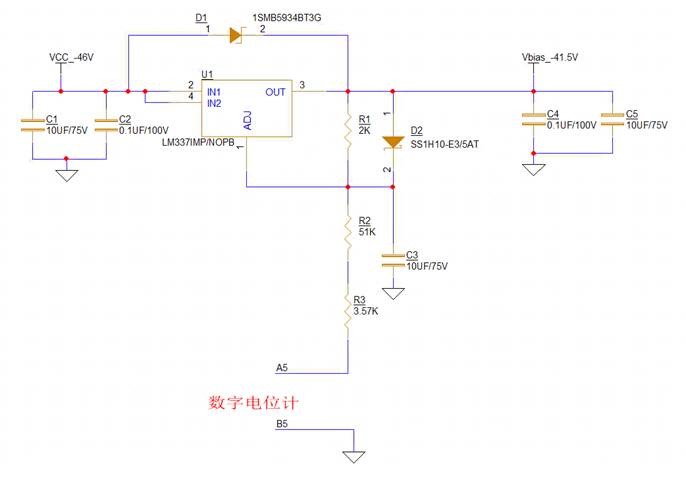

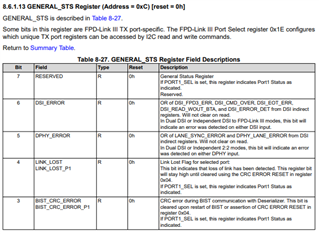

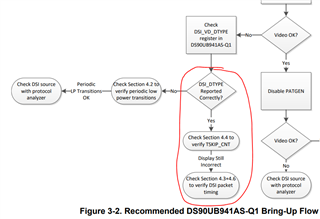

TI941部件异常

怀疑与 TI941配对问题;

(与大屏幕上的正常显示相比、TI 需要说明 DSI->TI941->TI948和 DSI->TI941->TI926信号路径对 DSI (DSI CLK/DSI 数据)的要求是否不同)

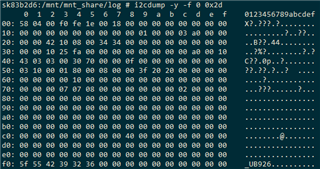

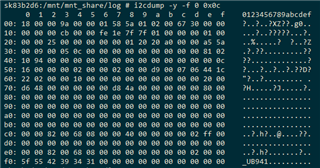

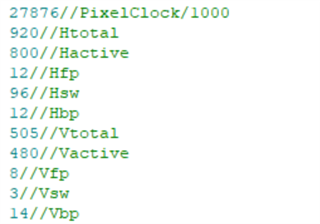

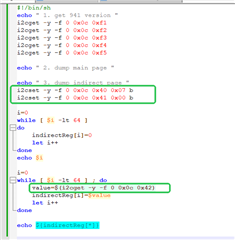

2. LT7911D DSI 输出配置为非同源模式

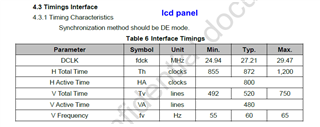

重复的闪光灯屏幕测量确认非同源模式下的 DSI CLK 在81MHz 周围。

在完全模式下、DSI CLK 频率约为83MHz、

TI 需要确认 DSI CLK 围绕81MHz。

TI941收集了屏幕闪烁的原因、

如果基于 DSI 时钟恢复像素时钟、

DSI 时钟偏置会影响恢复像素时钟频率、从而导致不同的帧速率、

但不应导致屏幕固定的闪屏;

3. TI926输出 HS 差分和内部恢复同步信号逻辑需要 TI 支持。

4.另外、TI948输出 LVDS 也具有 HS/VS、无论 HS/VS 逻辑是否相同