主题中讨论的其他器件:AM5716

工具与软件:

尊敬的 TI 团队:

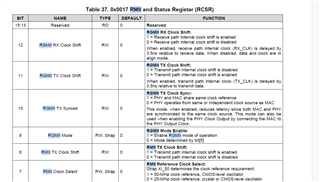

如何在 MII 模式下为 DP83822芯片设置 RX_CLK 极性反转?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嗨 Alvaro、

感谢您的支持。

RX 方向的速度非常低,约300kB/s )正常是约2.2MB/s (__LW_AT__通过 FTP 工具传输文件、 TX 方向的速度是正常的,链接没有中断。 故障率为10%、这是我们的根本问题。 这就是我们检查 MII RX 信号的原因。

让我来告诉您我们的调试操作。

将 RCSR(0x0017)位12从0设置为1后、RX 传输速率可以增加到大约2.2Mb/s、 波形显示建立时间为4ns。

因此、我们非常怀疑此低速是由建立时间不符合技术规格引起的。 4ns 仍然不符合 AM5716规范、如何设置建立时间>8ns。

尊敬的 Jie:

感谢您向该问题添加更多上下文并介绍所采取的调试步骤。

RX 方向的速度非常低 、约为300kB/s)正常情况下约为2.2MB/s (__LW_AT__通过 FTP 工具传输文件、 TX 方向的速度正常、链接尚未中断。 故障率为10%、这是我们的根本问题。 这就是我们检查 MII RX 信号的原因。[/QUOT]我同意此问题可能出在 MAC 接口内。

我们仔细检查了 DP83822设置 并发现它是在 RGMII 模式下而非 MII 模式下工作。需要确认的是、当 DP83822配置为 RGMII 模式时、一切都正常、没有问题。 只有在我们使用 MII 时才会出现该问题?

需要什么 MAC 接口? AM5716上的 MAC 和 DP83822都要配置在同一个 MAC 接口(本例中为 MII 或 RGMII)中、这一点非常重要。 例如、在 MII 模式下、PHY 同时提供 TX_CLK 和 RX_CLK。 在 RGMII 中、PHY 仅提供 RX_CLK、MAC 将提供 TX_CLK。

此致、

Alvaro

[/quote]

嗨 Alvaro、

很抱歉混淆您的、根本问题发生在 RGMII 模式。 自 问题发生以来一直采用 RGMII 模式、所需的 MAC 接口为 RGMII。

现在让我们来讨论 基于 RGMII 模式的问题。

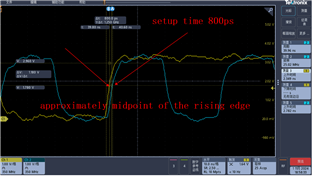

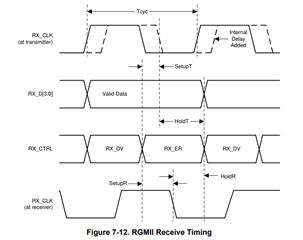

如果参考 RX_CLK 时钟上升沿、波形显示最坏的设置时间为900ps<1ns (RGMII 规格)、最好的时间可以为1.7ns>1ns。我怀疑这是问题所在、因此将 RCSR 寄存器的第12位从0设置为1可以修复该问题。

但我不确定数据是指 RX_CLK 的上升沿还是下降沿。

嗨 Alvaro、

是、启用 RGMII RX_CLK 移位(RCSR Reg 0x17[12])可以解决我们的问题。 您认为根本原因是未启用 RGMII RX_CLK 移位? 应启用或禁用 RGMII RX_CLK 移位?

另一个问题与波形相关。

当我们使用示波器来测量建立时间时、光标应该在振幅的50%或上升沿的中点对齐、对吧? 我们没有在标准802-3中找到介绍、如果您有相关的介绍文档、您能给我发送电子邮件吗? 我的电子邮件地址是: yinjie1@sungrowpower.com

尊敬的 Jie:

再次感谢您的确认。 是的、未启用 RGMII RX_CLK 移位是导致该问题的根本原因。 请保持启用状态。 我们希望时钟稍微落后于数据、以便在时钟的上升沿到来时、能够以正确的状态对数据进行采样。

在您共享的示波器捕获中、蓝色信号为 RX_CLK、黄色信号为 RX_CTRL 是否正确? RX_CTRL 应在 RX_CLK 的上升沿触发、看起来它在执行这个操作! 无论如何、如果在启用 RX_CLK 移位的情况下进行通信、我都不会再担心建立时间和保持时间。

此致、

Alvaro

嗨 Alvaro、

我同意。 我也认为这是根本原因。

但我仍然对规格有一些疑问。

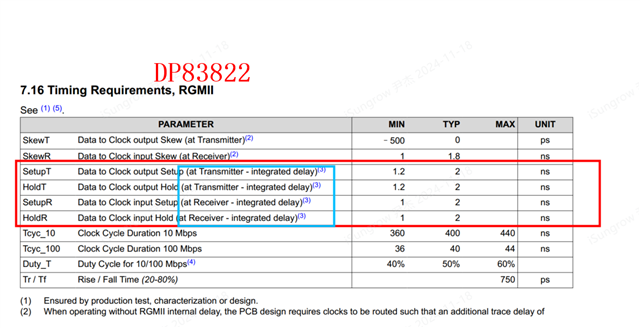

关于 DP83822规格的一个问题是"集成延迟"、如下面的蓝色框所示。 是指 PHY 内部延迟还是 MAC 内部延迟?

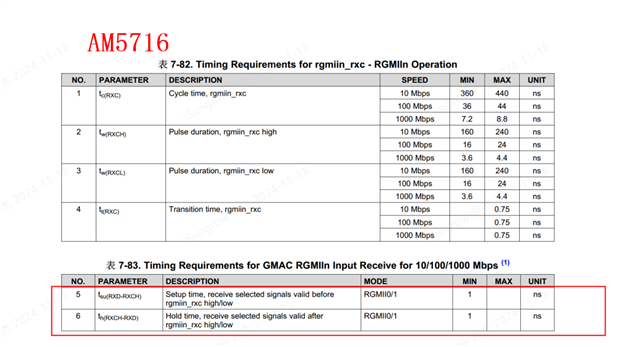

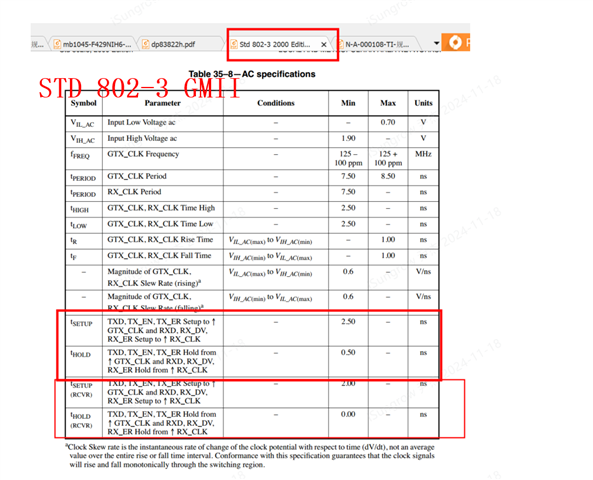

另一个问题是 AM5716规范与802-3标准之间的差异。 802-3标准显示设置/保持时间为2ns/0ns、上升/下降时间为1ns/1ns。 不过、AM5716规格显示设置/保持时间为1ns/1ns、上升/下降时间为0.75ns/0.75ns、这些差异让我感到困惑。 您能否评论一下。

注意:802-3标准中未提供 RGMII 规范、我只是指 802-3标准中的 GMII 规范。

尊敬的 Jie:

我很乐意 继续提供支持、您能否确认当前问题是否已解决、即您是否能够在设置了 RGMII CLK 延迟后成功发送数据?

[报价 userid="609388" url="~/support/interface-group/interface/f/interface-forum/1432236/dp83822i-how-to-set-rx_clk-polarity-reversal-for-dp83822-chip-in-mii-mode/5519669 #5519669"]关于 DP83822规范的一个问题是"集成延迟"、如下面蓝色框所示。 是指 PHY 内部延迟还是 MAC 内部延迟?这可能是指 DP83822或 MAC 都可能引入延迟。 我已经看到一些 TI 处理器在 TX_CLK 上具有无法禁用的默认延迟、因此应该禁用 DP83822上的 TX_CLK 延迟 (寄存器0x17[11]='0')、并且应该启用 RX_CLK 延迟(寄存器0x17[12]='1')。

规格比较通常会导致混淆、GMII 规格并非是同类的。 请在下面找到 RGMII 规格。 数据到时钟的延迟在标准中被称为 Tskew。

e2e.ti.com/.../2134.RGMIIv1_5F00_3.pdf

此致、

Alvaro