主题中讨论的其他器件:TDP0604、 TMDS181、、 TDP1204

工具与软件:

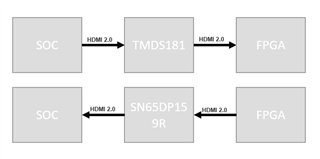

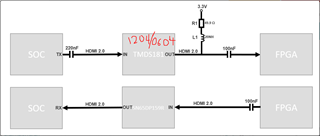

您好、请 kindy 帮助检查下面的 SN65DP159RGZT 和 TMDS181IRGZT SCH。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

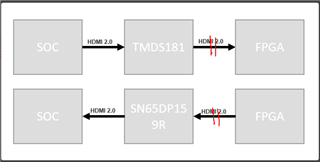

用于对 TMDS181的 HDMI 输出进行交流耦合的端接网络将产生减半的输出摆幅。 我建议使用 TDP0604而不是 TMDS181、因为 TDP0604可以接收直流耦合 HDMI 和内部偏置电流以实现交流耦合 HDMI 输出。 这将提高信号完整性。

您能换芯片吗? 此应用中是否需要重定时器、或者转接驱动器就足够了?

FPGA 似乎需要交流耦合、那么为什么 DP159没有交流耦合?

您好!

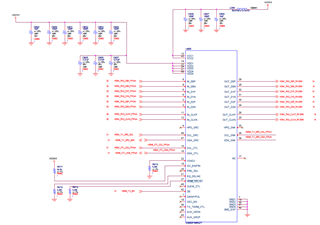

我还按如下方式更新了 pdf 文件。 请检查是否有。

尊敬的 David:

您能帮助检查下面的 SCH 吗? 我将 TMDS181更改为 DP159。 如有任何问题、请告诉我。

您好!

以下是原理图审阅

此外、对于 U4004:

将需要上拉至3.3V 以实现有效的直流耦合 HDMI 检测。 上拉后、需要使用交流电容器来传输交流耦合信号。 这将有效地将输出信号摆幅减半。 您需要更大限度地提高 SOC 的摆幅以对此进行补偿。 另一种选择是使用 TDP0604 (6Gbps)或 TDP1204 (12Gbps)、它可以接收和输出交流耦合信号并输出交流耦合输出信号。 这样就无需在 HDMI 线路上进行外部偏置。

SDA 和 SCL 是否不进入 SoC? 什么是 U17E

此外、对于 U4005:

有直流耦合 HDMI 连接到 RK3588 SoC 是否可以?

SDA 和 SCL 是否不进入 SoC? 什么是 U17E

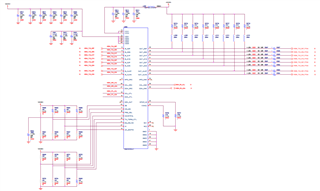

尊敬的 Vishesh Pithadiya:

对于 U4004、HPD_SRC;SCL_SRC/SDA_SRC;SCL_CTL/SDA_CTL 将连接到 RK3588 SOC(U1000)。 U17E 是 Xilinx FPGA。

对于 U4005、RK3588 HDMI TX 需要在 HDMI 2.0的交流耦合模式下运行。 但 U4005输入来自 FPGA 并输出到 RK3588。

BTW、U4004和 U4005是否都建议 切换为 TDP0604/TDP1204?

您好!

对于 U4004、我建议换用 TDP0604。

对于 U4005、请确保 SoC 能够处理直流耦合 HDMI。 如果 SoC 无法处理直流耦合 HDMI、我建议也将 U4005交换到 TDP0604。

请记住、TDP0604/TDP1204是转接驱动器、而不是重定时器。 这意味着不会有抖动清理。 这意味着布局要求将会更加严格。 我们非常愿意在电路板投入生产之前查看您的布局并对其进行审查。

尊敬的 Vishesh Pithadiya:

请 kindy 参考下面的更新 SCH。

BTW、我是否可以建议您将 EQ、TXPRE、TXSWG 设置设为默认级别?