工具与软件:

设置:

- 消息流 DP83867 Phy 。 RGMII 模式 .

- 观察 A 之间的差异 工作板 和 A 非工作电路板 .

- 侧重于自举引脚(例如、 RX_D0 、 RX_D2 、 RX_CTRL )和 MDIO/MDC 通信

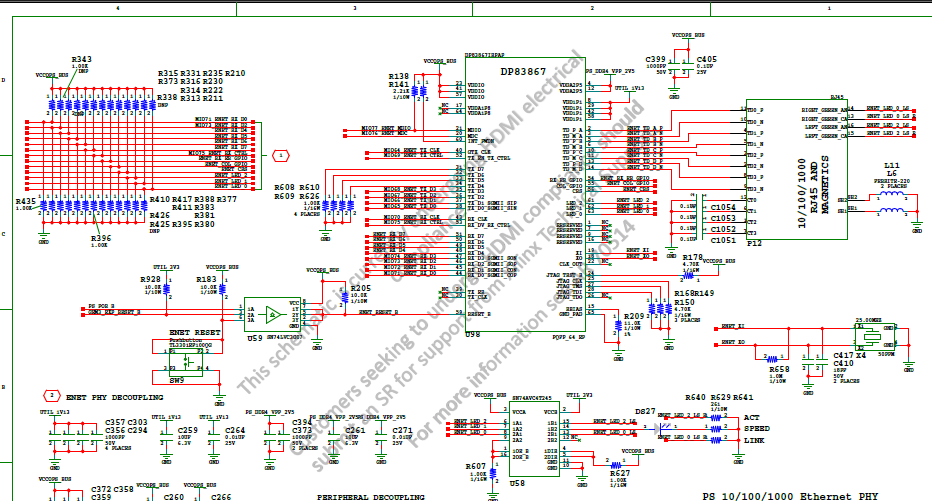

原理图:

上电观察结果:

- 工作板:

- RX_D0 一致性 低电平 提供内部上电和复位。

- RX_D2 一致性 低电平 上电期间、匹配预期行为。

- PHY 通过 MDIO/MDC 进行通信、并观察 MDIO/MDC 切换。

- 非工作板:

- RX_D0 正弦值 高电平 、即使它在原理图中被拉低。

- RX_D2 也是 低电平 、与工作板相匹配。

- MDIO/MDC 不切换、并且 PHY 对 MPSoC 命令无响应。

连接到 PC PHY:

- 尽管存在这些问题、但不工作电路板上的 PHY 成功建立了 100 Mbps 链路 与 PC 兼容。

- 通过 LED 观察 RX 活动、指示基本链路功能。

请求协助:

- 执行 VDDIO 相对于 VDDA 和 VDD1P1的电源时序 直接影响引脚搭接行为?

- VDDIO 的缓慢斜升是否会导致 PHY 错误地将 RX_D0锁存为高电平?

- 尽管原理图中使用了下拉电阻器、但 RX_D0仍为高电平的其他可能原因吗?