工具与软件:

您好、先生、

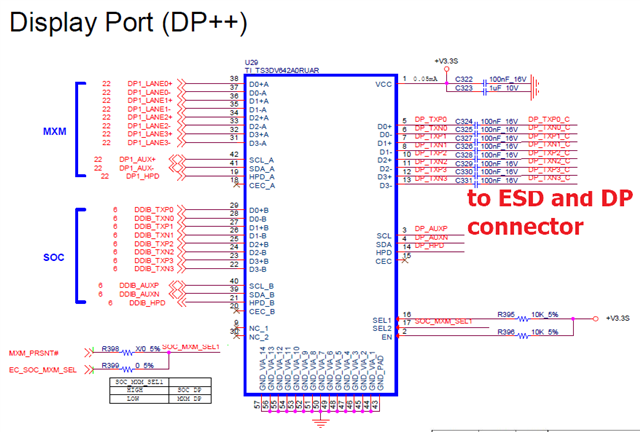

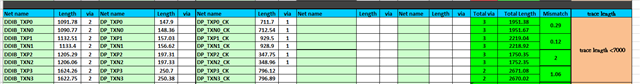

我们的主板使用 TI TS3DV642A0RUAR 切换来自 Raptor Lake-U (SOC)和 MXM 模块的 DP 信号。

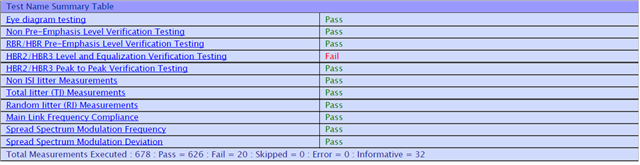

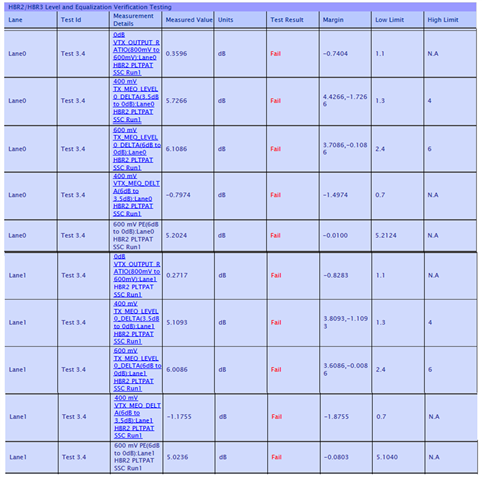

切换 Raptor Lake-U 的 DP 时、HBR2/HBR3等级和均衡验证测试存在 DP SI 问题

因为 DP 的长度不超过 Intel PDG 的最大长度。 这些 SI 问题可能不是由信号衰减引起的。

您是否有与 HBR2/HBR3等级和均衡验证测试的 SI 故障相关的经验?

您能就如何解决此 SI 故障问题提供任何建议吗?

对于从 TS3DV642A0RUAR 到 DP 连接器的过孔长度和数量、您有什么建议吗?