Other Parts Discussed in Thread: TPD2S703Q1EVM

工具与软件:

您好!

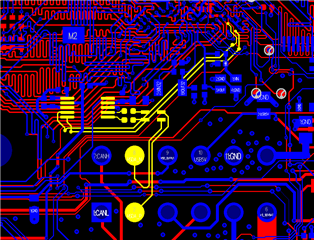

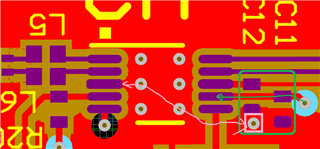

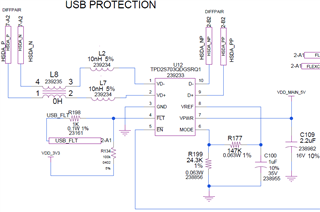

我们的 TPD2S703QDGSRQ1在已发布的产品中、最近我们遇到了一些电路板问题。

最初的数字很小、但现在我们注意到更多的故障、即高速通信中断。

基于上述设计、在工作电路中、Vmode =。 5V 和 Vref = 3.5V、

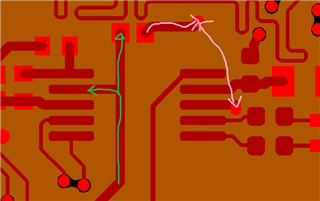

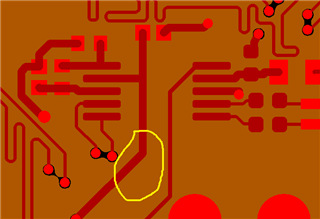

在故障电路中、Vmode 为0.64V、Vref = 4.57V。

您能否就会导致 Vref 跳转至4.57V 的原因提供专家建议?

谢谢!

Tony