工具与软件:

尊敬的 Hamzeh:

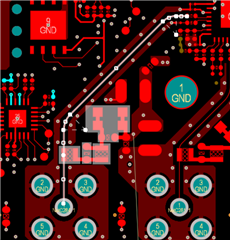

V3Link 布局的更改如下所示:

- 射频布线参考层更改为第2层而不是第3层、这会导致射频布线宽度减小到5.2mil。

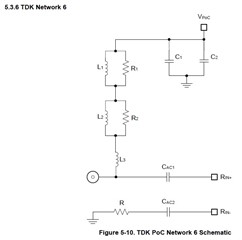

- 将 POC 网络从 TDK 网络5改为 TDK 网络6。

我们有以下问题:

- 如下图所示、我们已将所有 POC 网络组件放置在顶层。 我们的射频工程师建议将除 L3之外的所有 POC 元件放置在底层、以提高射频性能和边际测试结果。

- 我们已将射频布线周围的 GND 屏蔽布线间隙保持在每侧较远的3W (15.6mil)、并在 FAKRA 连接器的射频 TH 引脚处保留4W (20.8mil)反焊盘。

我们希望了解你在这里提出的建议和意见、以便进一步开展工作。