工具与软件:

您好!

我的客户面临着很少无法通过 MDIO 读取数据的问题。

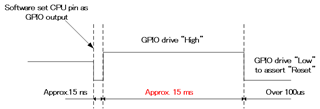

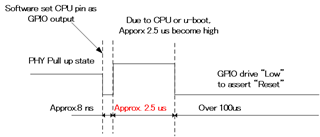

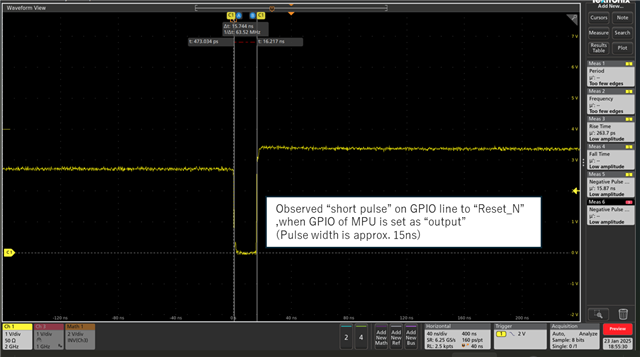

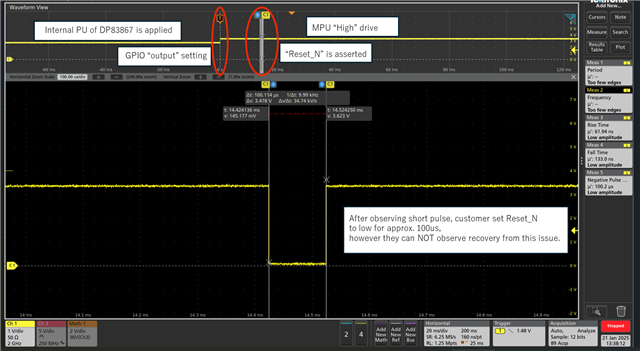

根据调查、他们在将 MPU 引脚设置为 GPIO 输出时、观察到从 MPU GPIO 线路到 DP83867IR 的"RESET_N"的短脉冲、如下所示。

观察到这个短脉冲后、即使他们将"Reset_N"设置为低电平持续100us、该问题仍然无法解决。

然后、客户有以下问题。

问题1。 根据数据表、您在下面针对"Reset_N"进行了描述。

"RESET 输入必须保持低电平至少1µs。"

然而、如果用户输入如此短的"低电平"脉冲至"Reset_N"、是否存在器件引起这种现象的可能性?

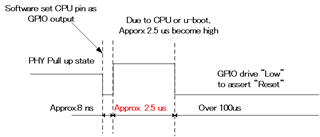

问题2: 客户变更电路。 它们在"RESET_N"线路上实现2.2千欧 PD、以消除 DP83867 "RESET_N"引脚的内部 PU 的影响。

之后、他们从未发现上述问题。 但是、他们希望了解您对这项工作的看法。

您能否提供有关此变通办法的反馈?

此致、