工具与软件:

大家好、团队成员:

特定链路伙伴出现通信问题。

在每200次的链路建立过程中、Ping 将不起作用。

根据寄存器信息、我们认为原因是自协商过程中出现了主设备/从设备不匹配。

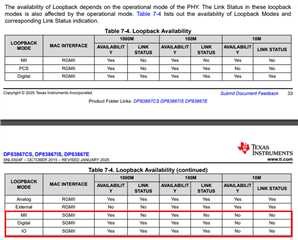

回送功能在确定主/从 不匹配的原因方面是否有效?

我已经就这一问题提出了几个问题、但问题尚未得到解决。

我们必须尽早解决这个问题。

DP83867IS:通信问题

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1447700/dp83867is-communication-problems

DP83867IS:关于寄存器0x000A 位[7:0]中的空闲错误计数器。

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1448230/dp83867is-about-idle-error-counter-in-register-0x000a-bit-7-0

此致、