工具与软件:

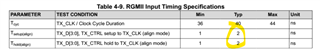

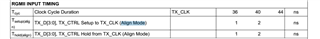

我打算设置100BASE-T1 RGMII 的内部延迟、TX 和 RX 延迟应在 PHY 侧设置。

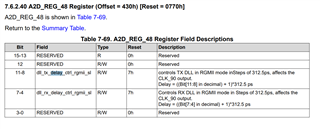

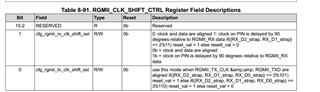

- 如果在 strap 设置期间使用了对齐模式、并且 cfg_RGMII_rx_clk_shift_sel=1b cfg_RGMII_tx_clk_shift_sL=1b

TX 和 RX 的 RGMII 内部延迟是多少? 仅2ns? 数据表仅显示2ns。

- 如果 在 strap 配置期间使用 RGMII (TX 和 RX 内部延迟模式)、

TX 和 RX 的 RGMII 内部延迟是多少? 5ns? 因为以下寄存器设置的默认设置:

DLL_TX_DELAY_CTRL_RGMII_SL:0xFh (5ns);

DLL_Rx_DELAY_CTRL_RGMII_SL:0xFh (5ns);

- CFG_RGMII_rx_clk_shift_sel cfg_RGMII_tx_clk_shift_sel 描述了如果设置为1b、则 clk 和数据之间存在90度。

- 如果使用 RGMII 对齐模式、则 TX 和 RXD 内部延迟为10ns?

- 如果 使用 RGMII (TX 和 RX 内部延迟模式)、那么 TX 和 RXD 内部延迟为15ns?