主题中讨论的其他器件:ISOW7741

您好!

有人能否解释为什么 ISOW7741下方的多边形在 EVM 中偏光? 这看起来是有意的。

谢谢!

John

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

有人能否解释为什么 ISOW7741下方的多边形在 EVM 中偏光? 这看起来是有意的。

谢谢!

John

尊敬的 John:

感谢您的联系。

是的、器件下方的区域特意没有任何铜线迹或多边形。 这对于保持应用的隔离额定值和爬电/间隙要求而言是必要的。 如果应用没有高隔离要求、则可以放宽这些要求、并在器件下方允许走线和多边形达到其认为适合其应用的程度。

线迹或多边形的存在不会影响 ISOW7741的运行或性能、这主要是应用隔离要求所需的。 谢谢。

如果您有任何问题、请告诉我、谢谢。

此致、

Koteshwar Rao

尊敬的 John:

感谢您寻求澄清。

只有器件主体下方的区域对于确定解决方案的爬电距离、间隙和隔离额定值至关重要。 器件引脚任一侧焊盘上的任何一点都没有约束。 这些迹线或多边形不会影响隔离额定值。

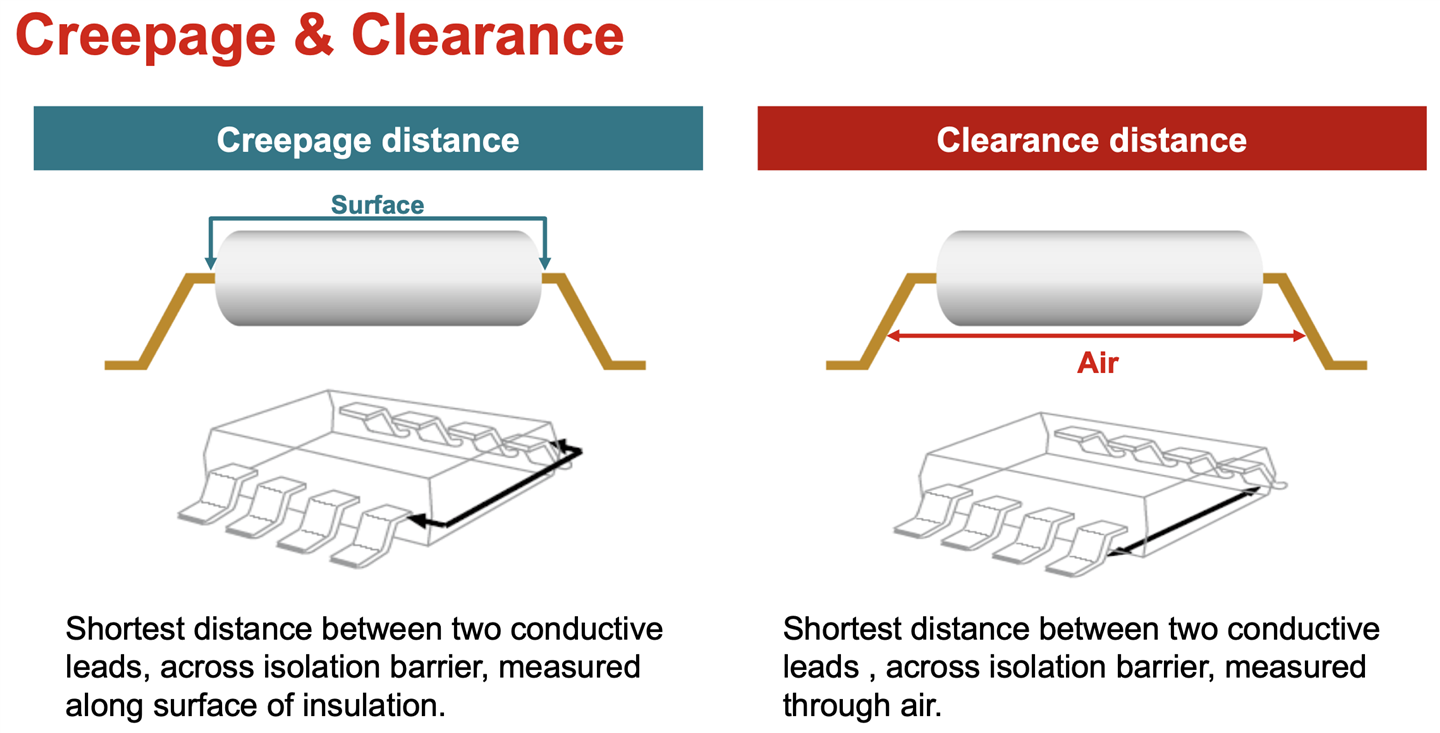

请参阅下图、该图描述了爬电距离和间隙、沿表面测量爬电距离、间隙通过空气。 在器件下引入线迹/多边形可以减小这些尺寸。 即使器件下方内层上的迹线和多边形也会影响整体隔离额定值、但与顶层和底层相比影响更小。

请告诉我这是否清楚并回答您的问题、谢谢。

此致、

Koteshwar Rao