Other Parts Discussed in Thread: ISO7741

如何计算数字隔离器支持的最大 SPI 速度?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

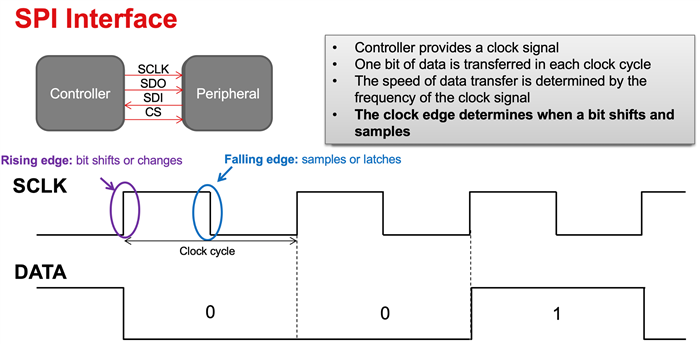

串行外设接口(SPI)是一种单主4线同步串行通信接口、涉及的4个信号为- SCLK、SDO (Pico)、SDI (POCI)和 CS\。 控制 器为所有外设提供时钟 SCLK、并且在每个时钟周期中传输一个位。 因此、SPI 接口的速度由 SCLK 的频率决定。

在 SCLK 的上升沿期间、数据变为需要传输的值、在下降沿期间、数据保持稳定、以便可以对其进行采样。 下图以图形方式显示了这一点。

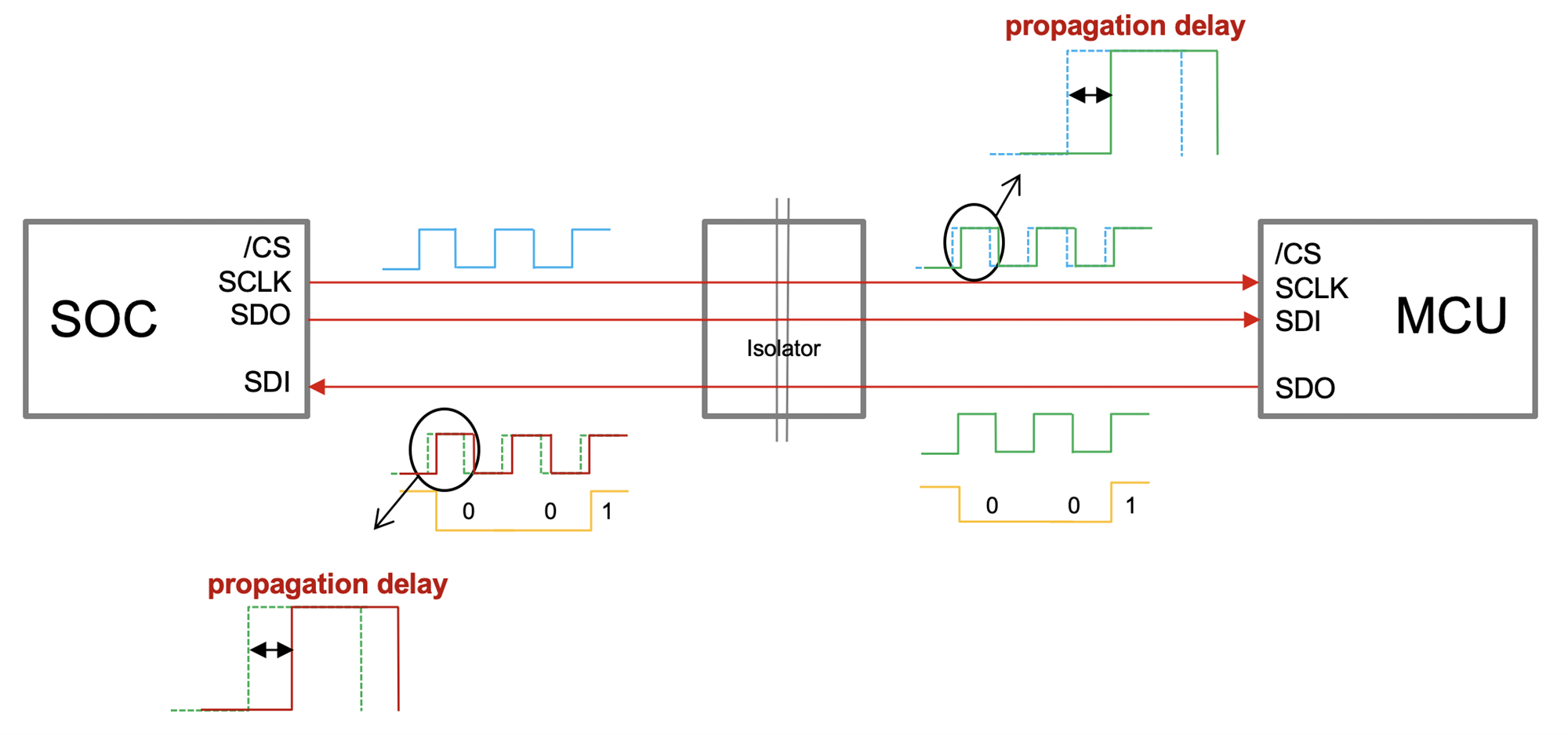

下图显示了 SoC 和 MCU 之间通过四通道数字隔离器进行的典型 SPI 连接。 下图还显示了传播延迟如何在通过数字隔离器时改变 SCLK、以及它如何影响正在接收的数据。

外设在 SCLK 的上升沿准备数据、 控制器在 SCLK 的下降沿对数据进行采样。 由于数据需要在半个 SCLK 周期内读取、并且 SCLK/SDOI 一起经历数字隔离器的往返传播延迟、因此最小 SPI 时钟周期或最大 SPI 速度可表示如下。

2 * tpd (max)< tSCLK (min)/2

换句话说、

fSCLK (max)< 1/[ 4 * tpd (max)]

例如、让我们考虑 ISO7741、在 VCC1 = VCC2 = 5V 时、tpd (max)为16ns。 在 ISO7741上可实现的最大 SPI 速度为 fSCLK (max)= 15.6MHz。