大家好、

1.89V < VCCI、VCCO < 2.25V 和1.05V < VCCI、VCCO < 1.71V 时、ISO67xxF 输出不确定。

我的客户担心 、如果 VCCI 或 VCCIO 缓慢上升或下降、输出可能不确定。

您能建议如何避免 输出不确定吗?

您能告诉我合理的斜升或斜降速率、以避免输出不确定吗?

UVLO 阈值 在数据表中指定、但 我在数据表中找不到详细的功能。

它是否与 数据表9.4中描述的断电(PD)状态类似?

此致、

伊藤

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

1.89V < VCCI、VCCO < 2.25V 和1.05V < VCCI、VCCO < 1.71V 时、ISO67xxF 输出不确定。

我的客户担心 、如果 VCCI 或 VCCIO 缓慢上升或下降、输出可能不确定。

您能建议如何避免 输出不确定吗?

您能告诉我合理的斜升或斜降速率、以避免输出不确定吗?

UVLO 阈值 在数据表中指定、但 我在数据表中找不到详细的功能。

它是否与 数据表9.4中描述的断电(PD)状态类似?

此致、

伊藤

您好,Darrah-San,

您能否详细说明不确定输出的确切定义?

我的客户不明白 VCCO=PD 时的输出是什么样子的。

它通常会像下面的线程中所讨论的那样悬空吗?

此外、如果1.89V < VCCO < 2.25V 或1.05V < VCCO < 1.71V、输出是否为中间电压(即高电平强或低电平强)?

此外还需要确保、当 EN=L 和5 1.89V < VCCI < 2.25V 或1.05V < VCCI < 1.71V 时、输出是否为高阻态?

此致、

伊藤

尊敬的 Itoh-san:

当器件因 VCCO = 0V 或非常接近0V 而断电时、大多数输出将悬空。 这是因为器件的输出电路的任何部分均未通电。 随着电源的增加、但仍处于低于器件上电所需电压范围(数据表中指定的范围)内、器件将保持断电状态、但部分输出电路可能会部分通电。 输出电路中的部分功率可能导致在输出端出现一些中间电压。 这就是我们将它们称为不可确定的原因、因为在斜降/斜升期间很难确切地知道器件电路的哪些部分已正确通电以及这将对输出电压产生怎样的影响。 在不确定状态下输出端出现的任何电压都将弱驱动既非高电平也非低电平的信号。

是的、当 EN=L 时、输出将为高阻态。 在高阻抗模式下、可使用上拉或下拉电阻器强制设置为高电平或低电平。

此致、

达拉

尊敬的 Itoh-san:

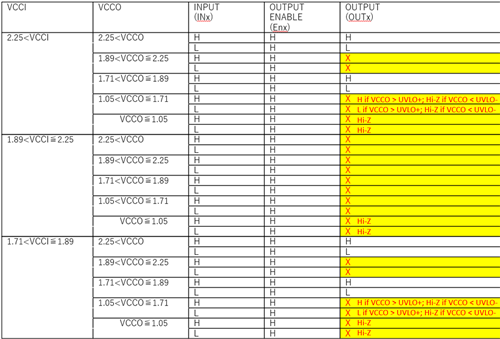

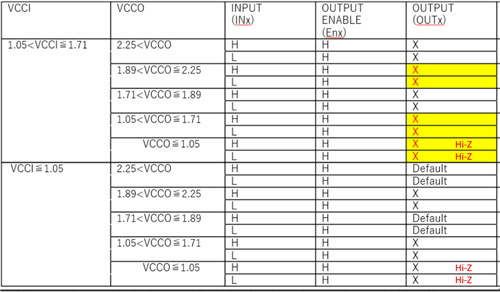

表格中的"X"是否用于指示不可确定? 如果是这种情况、则表格基本正确。 我在下面用红色做了一些更改。 当 VCCO < 1.05时、VCCO 可以视为已断电、输出将为高阻态。 当 VCCO 在1.5 < VCCO < 1.71范围内且 VCCI 在工作范围内时、输出将取决于器件的特定 UVLO+和 UVLO-。 UVLO+和 UVLO-将在1.5V 至1.71V 的范围内、因此整个范围将不会有相同的行为。

输出不确定的原因是 VCCO 侧仅部分通电、因此尽管输入信号可以按预期通过隔离栅接收和发送、但输出电路可能无法按预期输出信号。 隔离器的两侧独立工作、因此在 VCCO 断电时、输出信号状态不受输入状态的影响。

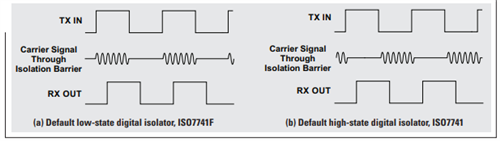

F 型和非 F 型数字隔离器的载波信号行为不同。 对于 F 器件、当输入信号为高电平时、载波信号为"打开"(发送正弦信号);当输入信号为低电平时、载波信号为"关闭"(不发送正弦信号)。 对于非 F 器件、当输入信号为低电平时、载波信号为"开";当输入信号为高电平时、载波信号为"关"。 因此本质上、当输入信号与器件的默认输出相匹配时、载波信号将关闭。 如有任何疑问、请告知我。

此致、

达拉

您好,Darrah-San,

是的、X 表示不可确定。

我想对您补充的几点内容进行讨论。

首先、您应该说、如果 VCCO<=1.05V、那么输出将是高阻态。

它与数据表中的表9-2不同(定义为不可确定)。

您能详细说明一下吗?

此外、我认为、如果1.05V<VCCO<=1.71V、您刚才提到输出将是不确定的、这意味着需要中间电压(H 也不是 L)。

我认为直接显示"H if VCCO>UVLO+; Hi-Z if VCCO<UVLO-"有点令人困惑,所以我认为最好把它保持为"不可确定"。

"你怎么知道的?

我了解 OOK 部分。

此致、

伊藤

尊敬的 Itoh-san:

当输出电路完全断电时、会出现高阻态输出。 这种情况在0V 至可能的1.05V 范围内发生。 数据表中的表9-2对器件行为进行了更笼统或概括性的介绍。 实际上、器件的行为稍微复杂一些、因为阈值会因器件而异。 为了更直观地了解器件输出、表9-2是正确的。

我同意这一区别以及添加 UVLO+和 UVLO-可能会让人困惑。 为简单起见、将桌子保持原来的样子就可以了。

此致、

达拉