请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ISO1050 尊敬的技术支持团队:

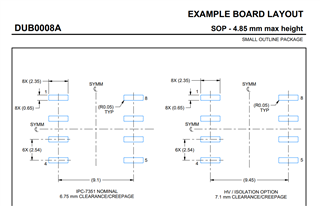

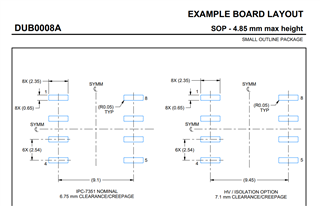

ISO1050DUBR 的"IPC-7351标称6.75mm 间隙/爬电距离"和"HV /隔离选项7.1mm 间隙/爬电距离"之间有何区别?

我通常应使用哪种焊盘图案? 对于隔离规格、"HV/隔离选项"是否更适合?

在这种情况下、请告诉我数据表的具体规格。

此致、

TTD

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的技术支持团队:

ISO1050DUBR 的"IPC-7351标称6.75mm 间隙/爬电距离"和"HV /隔离选项7.1mm 间隙/爬电距离"之间有何区别?

我通常应使用哪种焊盘图案? 对于隔离规格、"HV/隔离选项"是否更适合?

在这种情况下、请告诉我数据表的具体规格。

此致、

TTD

您好、TTD:

不同之处在于7.1mm 间隙和爬电距离焊盘图案提供了有关如何增加隔离栅上导体的最短侧到侧距离的建议。 在这种情况下、需要更高的工作电压要求。

这不会增加隔离等级或器件本身的性能、而是会横向增加、以根据系统级工作电压要求消除封装产生电弧的可能性。

有关爬电距离和间隙的更多详细信息、可在此处找到:

https://www.ti.com/video/5778857780001

此致!

迈克尔