您好!

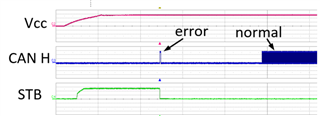

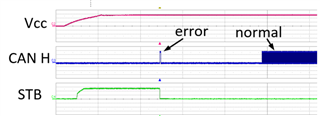

我发现当部件上电时、在等待 RX/TX 激励之前、CAN 输出切换一次。 这种情况在电源启动时发生。 最初、STB 引脚连接到地。 然后、我将 STB 引脚拉低了大约100ms、脉冲随 STB 移动。 这个加电脉冲有时会在 PC 工具中导致错误、所以我想办法解决这个问题。

我用+5V 为 VDD 供电、用+3.3V 为 VIO 供电。 3.3V 是源自+5V 的 LDO、因此它们可以有效地组合在一起。

谢谢!

特洛伊

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我发现当部件上电时、在等待 RX/TX 激励之前、CAN 输出切换一次。 这种情况在电源启动时发生。 最初、STB 引脚连接到地。 然后、我将 STB 引脚拉低了大约100ms、脉冲随 STB 移动。 这个加电脉冲有时会在 PC 工具中导致错误、所以我想办法解决这个问题。

我用+5V 为 VDD 供电、用+3.3V 为 VIO 供电。 3.3V 是源自+5V 的 LDO、因此它们可以有效地组合在一起。

谢谢!

特洛伊

您好、Troy:

感谢您的耐心等待、

我能够测试 EVM 来复制您观察到的脉冲、但我无法重新创建。 请参阅下面的波形以及测试设置详细信息。

VDD = VIO = 5V

采用1%到50%的各种占空比测试了 STB =脉冲序列、频率经测试为1kHz 和100Hz

CH1 = STB

CH3 = CANH

从上面的波形可以看出、当 STB = LOW 时、CANH 默认保持隐性(~2.5V)、当 STB = HIGH 时进入 Hi-Z。 当 CANH 为 Hi-Z 时、该电压会降至0V、一旦 STB 变为低电平、该电压便会恢复到~2.5V。 我没有在您的波形中看到该预期行为、也没有在波形中看到任何时序详细信息。 请务必提供与您的测试条件相关的更多信息、以便我可以确认我的测试是否与您的匹配、如果不匹配、我可以尝试重新创建您的测试条件。

期待收到您的意见、谢谢。

此致、

拉奥·科特什瓦尔

您好、Troy:

感谢您提供的输入和波形。

我想重现此问题、并且为了让我能够做到这一点、我将提供具体的详细信息、以便我可以使用完全相同的条件进行测试。 具体信息、例如 ISOW1044的 VDD 从0V 到5V 的斜坡时间是多少、STB 保持在低电平或高电平后几微秒或几毫秒、以及此事件后 CAN 总线上发生毛刺脉冲数。 显示时间和电压刻度的波形应提供此信息。

请注意、务必监控器件电源、以重现并调试该问题。 我知道您可能通常会监控整体系统电源、但这并不能告诉我 ISOW1044是否同时加电。 因此、它有助于直接监测 ISOW1044的 VDD。

如果没有这些信息、我尝试重现故障可能不会成功。 也可能只有您的样品表现出这种行为、而不是样品表现出这种行为。 为了得出结论、我需要相同的测试条件。 如果在相同的测试条件下、我无法在样片上重现问题、我可能会要求您将样片发送给我、以便我可以进行测试并尝试了解原因。 谢谢。

此致、

拉奥·科特什瓦尔

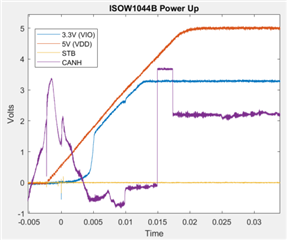

Koteshwar、

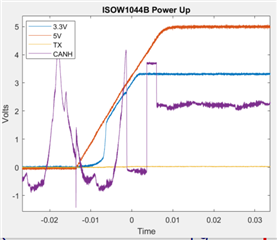

此处的图显示了5V (VDD)、3.3V (VIO)、STB (直接接地)和 CANH (引脚19以引脚11为基准)。 在电源应用之前、CANH 看起来像是高阻抗、探针拾取60Hz。

CANH 变为高电平大约2.3ms、然后再设置为2.5V。

这是同一测试集的缩小图、显示 CAN 流量在第一个 CANH 脉冲之后大约205ms 开始。

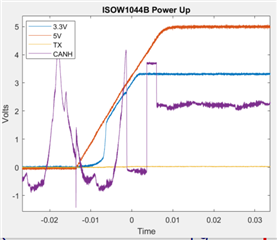

此测试集与探测 TX (引脚3)不同、而非 STB。 它显示当 CANH 变为高电平时、在设置为2.5V 前它是平坦的。

这显示了 RX 对 CANH 高电平状态的响应。

我意识到数据表建议在 TX 上使用外部上拉电阻器、现在我将下拉电阻器。 这会导致问题吗? RX 上没有外部上拉电阻器。

感谢您的支持。

特洛伊

您好、Troy:

感谢您分享输出脉冲的详细波形、连同电压和时间标度、这有助于我更好地了解这个问题。 请允许我在相同的加电条件下测试 EVM 以重现问题、并就此问题与您联系。

在此波形捕获期间、TX 是保持低电平还是悬空?

低 TX 应该会使 CAN 总线变为显性、但我看到它是隐性的。 TX 引脚也是使用500kΩ 电阻在内部上拉的、当输入悬空时、该电阻也会变为显性状态。

我意识到数据表建议对 TX 使用外部上拉电阻器,但我正在下拉电阻器。 这会导致问题吗? RX 上没有外部上拉。[/报价]TX 引脚上的外部上拉是可选的、因为器件具有内部上拉。 为了器件的可靠运行、RX 上的上拉电阻器也是可选的。

请允许我在与您相同的测试条件下提供测试和观察结果来与您联系。 谢谢。

此致、

拉奥·科特什瓦尔

您好、Troy:

感谢您的确认。

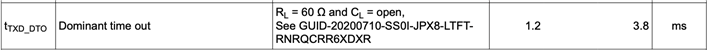

CAN 标准要求 CAN 总线在不使用时保持隐性状态(逻辑高电平)、仅在总线上传输数据期间变为显性状态(逻辑低电平)。 在所有其他时间、它应保持隐性状态(逻辑高电平)。 如果总线意外地被强制进入显性状态(低电平)超过1.2ms、则显性超时(DTO)将开始生效、将 CAN 总线从显性状态释放、并强制其进入隐性状态。 数据表中 DTO 的额定值如下所示。

我看到您在使用4.99kΩ 的下拉电阻器使 TX 保持低电平(显性)。 因此、输出首先变为显性状态(显性=> CANH = H;CANL = L)、当 DTO 启动时、它会变为隐性状态(隐性=> CANH = L;CANL = H)。 这是预期行为。 在您的波形中、您还可以注意到、CANH 保持高电平大约3ms、这与数据表中的 DTO 规格相符。

建议不要使用电阻器下拉 TXD 引脚、而应将其上拉并在数据传输期间仅驱动为低电平。 ISOW1044的 TXD 具有内部上拉电阻器、因此外部上拉电阻器是可选的。

根据上面的说明、可以清楚地看出这不是问题、而是器件的预期行为。 请检查这些信息、如果有任何不明确的地方、请告诉我。 谢谢。

此致、

拉奥·科特什瓦尔