https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1500727/txs0108e-txs0108e

器件型号:TXS0108E主题中讨论的其他器件: TXU0104

工具/软件:

我正在使用 TXS0108E、并观察到了一些预期行为:

1.我设置的 VCCA = 1.8V 且 VCCB = 3.3V、但 B 侧输出的幅度为2.5V -我期望的是3.3V。

2.我已将 TXS0108E 的 A 侧连接 到 FPGA 1V8组、并已确认器件 A 侧的逻辑值正确、但一些等效 B 侧输出具有相反的逻辑状态-这不是我预期的那样。

在所有情况下、OE 都已上拉至 VCCA 以启用所有 I/O

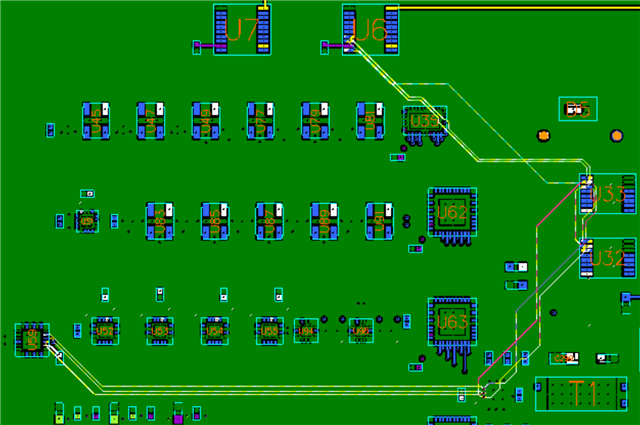

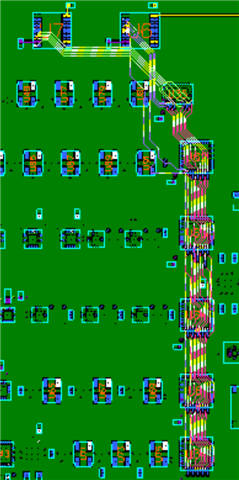

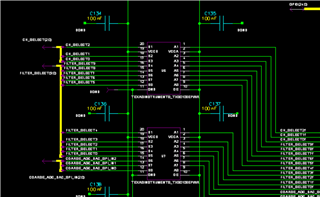

我的原理图如下:

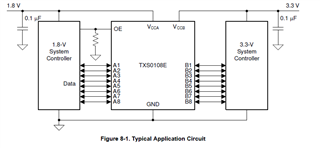

我认为我的原理图与数据表中的下图相同

请建议...

谢谢你