请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC3G17 工具/软件:

您好!

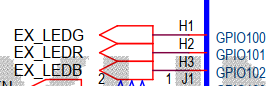

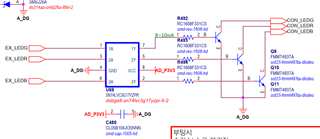

在下图中、EX_Ledg、EX_LEDR 和 EX_LEDB 连接到 MCU 的 GPIO (28388DZWT)。 在 MCU 复位和引导之间的短暂时间(大约小于100ms)内、MCU 的 GPIO 输出处于开漏状态。 在此状态下、SN74LVC3G17 IC 的输入实际上保持悬空(开漏)、但其输出变为高电平。 为什么会发生这种情况?

在此从复位到引导的转换期间、电路会短暂地意外激活。 对于 SN74LVC3G17、当输入保持悬空(开漏)时、输出变为高电平是否正常? 在此期间是否有办法将输出置为低电平?

此致、