工具/软件:

你(们)好

在 VCC > VDD 的模式下运行时、CD40109将用作高电平转低电平转换器。 在这种情况下、"使能"引脚的逻辑电平是多少?

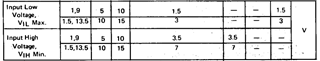

事实上、我不能100%确定这个逻辑水平通常是多少-例如(0.7*/ 0.3*) Vdd? 我不理解表的下半部分"静态电气特性"。

例如、"Vo"栏和"1,9"条目:"1,9"表示什么? -我假设 Vo 必须短路电压输出。

在我的例子中、我有2个芯片:

- 其中一个充当5V (输入)-> 9V (输出)。

- 其中一个输入的电压为9V (输入)-> 5V (输出)。

这里的使能逻辑电平是多少。 两种情况下5V 是否都正常、或者情况(2)是否需要9V?

此致

Stephen