主题中讨论的其他器件:SN74HCS74

工具/软件:

尊敬的 TI:

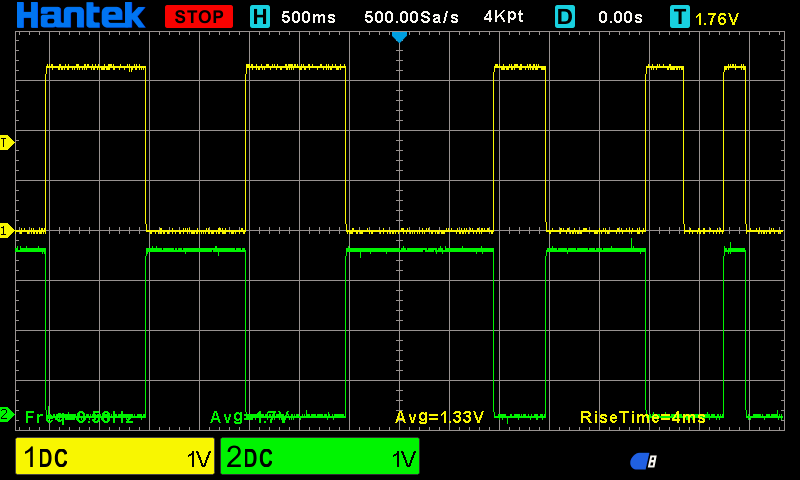

我在 设计中使用的74LVC1G175有问题。 在研究其行为后、我发现它不仅会改变时钟输入的上升沿上的输出、而且也会改变下降沿的输出。黄色的顶部曲线是时钟(引脚1)、底部绿色是输出(引脚4)。

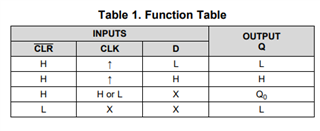

SN74LVC1G175DCKR 数据表中的真值表图片、从中可以看出只有上升沿才会导致输出变化。

我不确定是否有我应该了解的具体细节? 它由3.3V 电源供电、作为切换 F-F 耦合、其中 N 沟道 MOSFET 连接在输出端和数据输入端之间。

提前感谢。