https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1507251/tpld-ics-logic-forum

器件型号:TPLD-ICS主题:TPLD1202中讨论的其他器件

工具/软件:

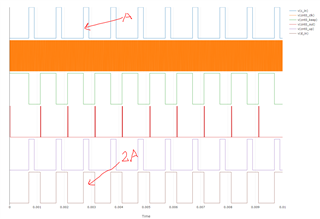

如何通过输入占空比为 A?的方波、在 TPLD_1202上生成占空比为2A 且相位为 A 的方波

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1507251/tpld-ics-logic-forum

器件型号:TPLD-ICS工具/软件:

如何通过输入占空比为 A?的方波、在 TPLD_1202上生成占空比为2A 且相位为 A 的方波

谢谢!

尊敬的 f j:

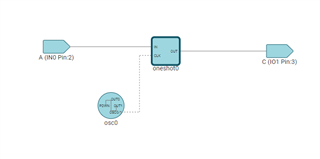

您可以使用计数器和 DFF 实现接近效果。 请参阅 TPLD1202上的以下电路:

我已将电路连接到此消息。

e2e.ti.com/.../3058.pulsething.syscfg

此致、

Malcolm

尊敬的 FJ:

如果您知道 TON 有多长、就可以使用单稳态且具有适当的输入时钟频率。 示例:

FJ、

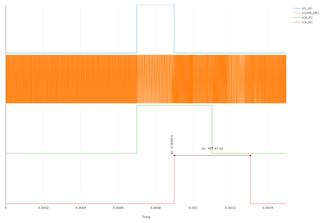

尝试此电路。 我复制了它并添加了一些额外的逻辑。 也许这是您之前所做的。 您只需调整计数器数据和时钟速度即可获得所需的占空比。 下面是一个仿真示例:

是的、输出脉冲宽度非常略长于2A (7 μ s、或者由于计数器的工作方式、约为7个时钟周期)。 基本上、输出脉冲将始终比2A 长~3.5%(即最终输出将始终为2.035A)。 希望这个裕度符合您的规格。 如果不是、那么我看不到使用 TPLD 实现这一点的好方法。 总是会有轻微的延迟

e2e.ti.com/.../pulsefalling.syscfg

对于占空比<1/3、=1/3、>1/3的其他情况、我们可以实现这一点、但在结束脉冲宽度始终比您希望的略长的情况下、这一点与之类似。

此致、

Malcolm