请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC1G74 工具/软件:

我将使用 SN74LVC1G74 D 型触发器 IC。 我面临的问题是输出 Q 行为不符合预期。 具体来说:

- 当 有用 并且 先生 (主复位)输出清零(高电平) Q 输出为低电平

- 但在清除之后 先生 (将其设置为低电平)、如果我启用 有用 低电平(下降沿)、输出 Q 这是意外的。 我预计它会变低。

以下是我执行的步骤:

| 数据 | 先生 | 有用 | 输出 (Q) |

|---|---|---|---|

| H. | H. | 驱动至低电平 | 驱动至低电平 |

| H. | H. | 发送到 DOUT 上 | 高电平 |

| H. | l | 高电平 | 驱动至低电平 |

| H. | H. | 高电平 | 驱动至低电平 |

| H. | H. | 保持一致 | 高电平 |

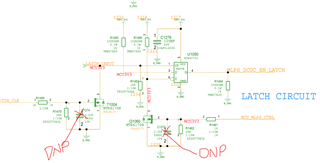

这是电路

这是电路