https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1547186/tlv803e-tlv803ea26dpwr

器件型号:TLV803E工具/软件:

尊敬的团队:

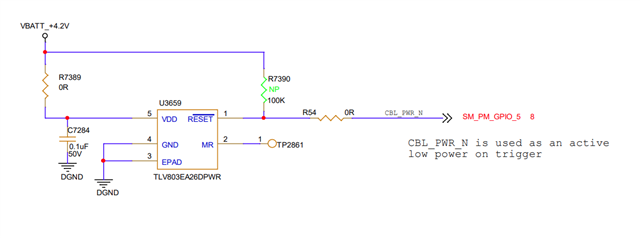

我 在设计中使用了器件 TLV803EA26DPWR、其中在单次下电上电期间提供 VDD 时、需要一个低脉冲。

我的系统需要一个低电平脉冲作为启动的触发器。

为 VBATT_+4.2V 供电时、系统会遇到以下序列:

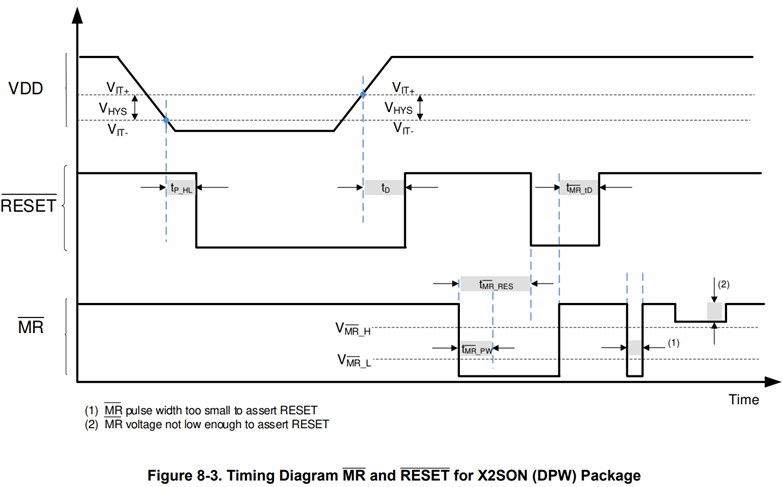

VDD < VPOR - RESETn 的未定义状态

2.VPOR < VDD < RESETn - VIT 将稳定低电平信号

VDD≥ RESETn - VIT 将稳定低电平信号

4.RESETn≥VIT RESETn+- VDD 将稳定 高电平信号

在数据表中、表 8-1 第四行 VDD 条件((VDD≥<xmt-block2>VIT</xmt-block>–)是否VIT是否存在拼写错误?

另外、请让我了解对上述顺序的理解。