主题中讨论的其他器件: SN74HCS595

工具/软件:

你(们)好

我需要 16 个额外的 GPIO 来每个驱动一些 SSR、需要 5mA

我计划使用 SN74HCS595、但 SN74HCS594 与此 devi Post 有何不同 ? 我相信两者都是不相容的。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

你(们)好

我需要 16 个额外的 GPIO 来每个驱动一些 SSR、需要 5mA

我计划使用 SN74HCS595、但 SN74HCS594 与此 devi Post 有何不同 ? 我相信两者都是不相容的。

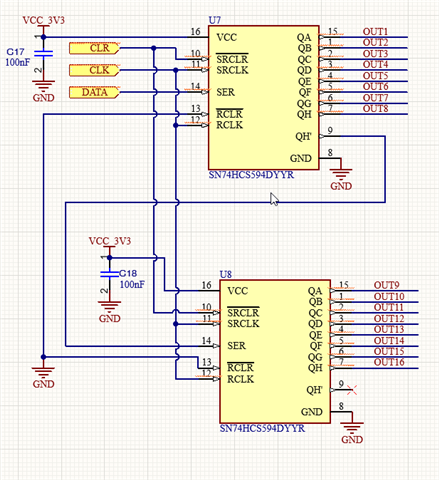

至少需要多少个 GPIO 引脚才能控制输出? 我正在使用这些器件生成额外的 GPIO 输出。 我将使用两个串联电阻来创建 16 位输出。

能否先组合 (SRCLK 和 RCLK)、将 OE 设置为低电平、然后将 SRCLR 设置为另一个 GPIO 、因此我们有一条时钟线、一条 SRCLR 和 ON 数据、总共 3 个 GPIO?

这样、当我设置该位时、它们也在时钟的下降沿输出。 是否也有办法做到这一点? 每次需要更改 GPIO 时、只需执行 CLR 和复位、并将之前的引脚更改为上一级、并执行 16 个时钟周期。

这是目前的电路图、请注意、符号对应 594、但我将使用 595

是否可以仅将最终 IC 上的引脚用作额外的 GPIO 引脚?

此外、如何确认输入到器件中的数据从输出 A 开始、我是否始终需要确保有 16 个 CLKS、并且 SRCLR 会将计数器复位为 0? 这是为了确保数据输入和输出之间不会不同步、或任何形式的不匹配。

在复位过程中、我可以将输出后的数据设为 0、即 16 个时钟、再设为任意值

谢谢。

选项 2 会更好、即减少一个 GPIO。

数据表显示了具有 RC 电路的引脚 10 (SRCLR)。 这是否必要? 该引脚是否可以直接连接到 3.3V? 引脚 13 可以连接到 GND 吗?

我将使用其中两个器件、提供 16 个信号。 然而,有一个可能性,我可能需要 17。 我是否可以在最后一个器件上使用 QH'(引脚 9)、使用 2N3904 晶体管对其进行反转并将其用作我的第 17 个信号? 这是否可行?

我计划使用 SN74HCS595、而不是 SN74HCS594、但我相信器件是兼容的;只是我的 PCB 符号是 SN74HCS594

因此、引脚 13(当前为低电平)将是 OE、如果我正确、对于任何输出、该引脚需要为低电平?