工具/软件:

您好、

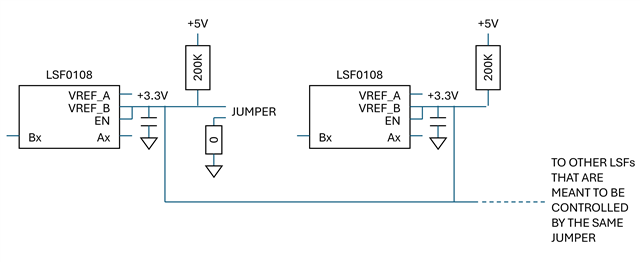

我想使用相同的跳线启用和禁用多个 LSF0108s。 我相信我已经正确偏置了 LSF0108、以便在插入跳线时可以将其禁用、但是如果多个 LSF0108 之间的 VREF_B 和 EN 引脚在要启用时短接在一起、是否存在任何问题? VREF_B 或 ENS 之间可能会以某种方式发生争用?

谢谢、

Matthew

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Matthew、

我建议不要这样做、因为通过这种方式启用每个 LSF 后、总漏电流会增加、并导致 VREFB + EN 节点出现波动、从而可能导致转换问题。 如果在不同的时间是 EN/DIS、则每个 LSF0108 的 EN 引脚都应具有自己的开漏驱动器。

此致、

插孔

嗨、Jack、

感谢您的推荐。

为了确保我们在同一个页面上、我们希望启用所有 LSFS 或禁用所有 LSFS — 我们不会尝试在禁用其他 LSFS 的同时启用某些 LSFS。

我有点困惑的是、 虽然总漏电流会随着以这种方式启用每个 LSF 而增加、但我计划使用共享 VREF_B + EN 引脚为每个 LSF 添加一个 200K 欧姆的上拉电阻、如图所示。 这是否应该会导致节点偏置到与未连接到其他 LSFS 时相同的电压? 转换时、这些引脚上是否消耗某种动态电流、这会导致与其他 LSFS 发生争用?

谢谢、

Matthew