Other Parts Discussed in Thread: SN74HC165

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号: SN74HC165

您好!

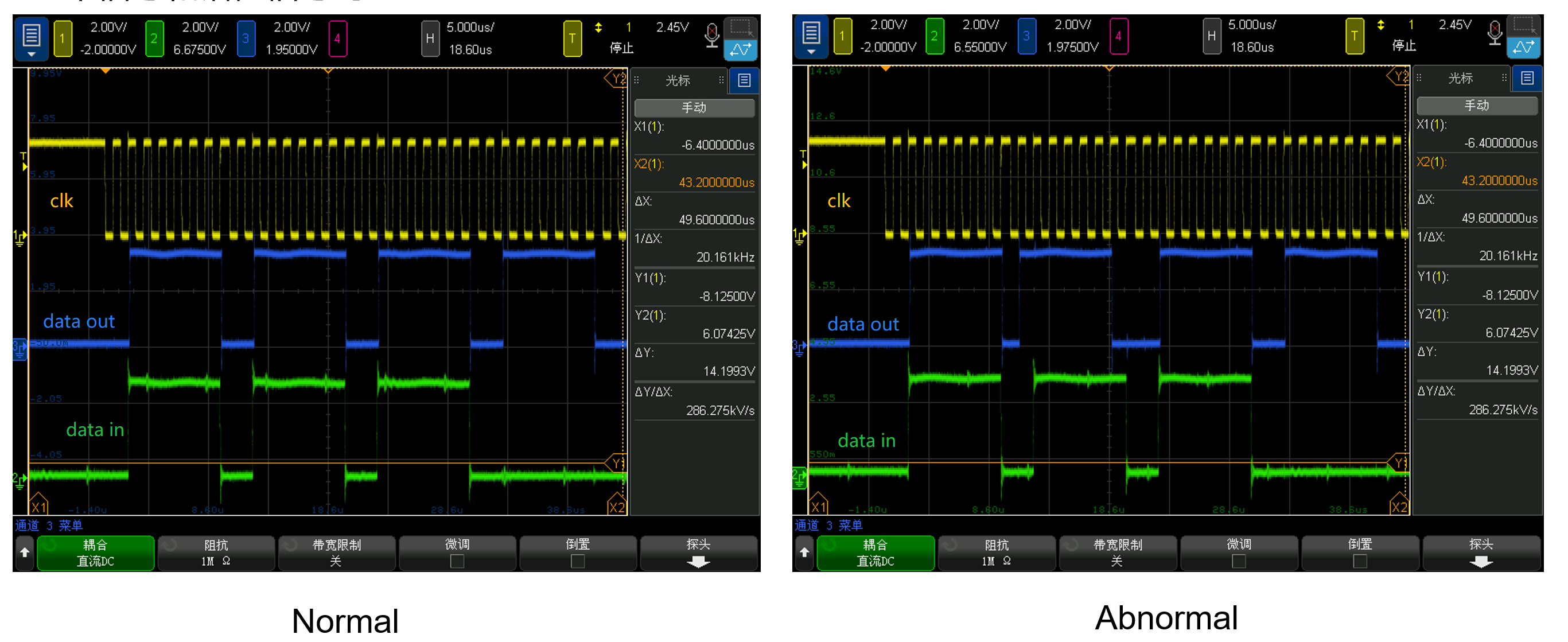

我的设计中有 8 个 SN74HC165 串联、可获得 48 个 IO 状态(每个 IC 6 个 IO)。 机箱中的每根电缆约为 500mm。 大多数情况下、它们运行良好、但其中一个芯片存在问题。 当数据通过它并被输出时、它会错误地移位。 正常数据应该是 00111111、但通过它后变为 01111110。 更换芯片后问题得到解决。 现在、我们的客户想知道为什么会发生这种情况。