Other Parts Discussed in Thread: SN74LVC1G373

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1593647/sn74lvc1g373-output-status

器件型号: SN74LVC1G373

尊敬的专家:

客户当前正在使用 SN74LVC1G373 进行开发、并且遇到一些问题。 他们希望得到解决这些问题的援助。 谢谢你

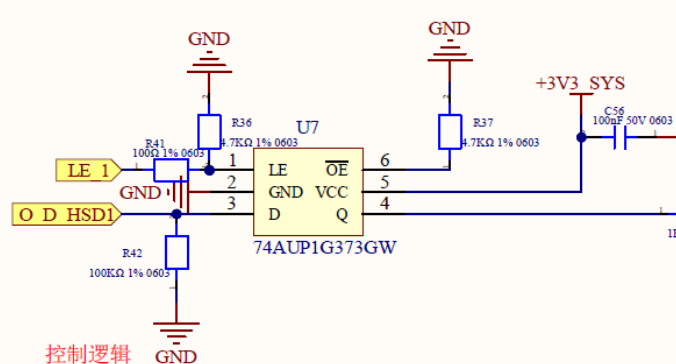

1、电路如下:D、LE、OE 引脚默认被拉低、MCU I/O 可以控制这三个引脚;测试发现、每次芯片复位重启后、芯片的 Q 输出保持高电平。 这是正常的吗? 之前、我看到了相关信息、指出锁存器的默认输出不确定、而它们的实际测试显示为高电平输出

2.客户希望实现这样一种状态:锁存器的输出是 MCU 复位前芯片锁存器的 D 状态、并且锁存器的输出不受 MCU 复位的影响。 可以实施该芯片吗? 目前、无法实施客户测试。 我们希望提供一些建议。 谢谢你