线程中讨论的其他部件: SN74LVC2T45

大家好,团队

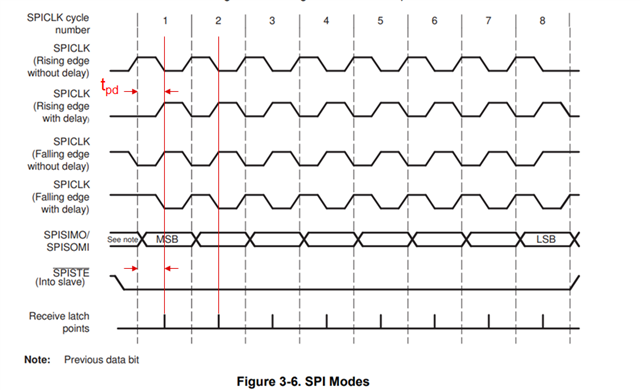

尽管信号传播延迟= 0.5~10ns,为什么我们可以使用200Mbps 数据速率@ 3.3V 到5.5V 电平转换?

SPI 主输出时钟为200MHz (来自200Mbps),等于一个周期5ns。 但是,TXU0304-Q1的传播延迟为0.5 ns~10 ns,用于5.0伏到3.3V 的转换@TA=125C,如“7.11切换特性 VCCA=3.3+- 0.3”中所示。 它会导致传播延迟>时钟周期,看起来操作不正确。

此致,

Ochi